基于FPGA的星載計算機自檢EDAC電路設計

SEU造成的RAM單元1比特錯誤如果不定時清除,就會產生累積,使計算機由此處理的結 果產生出2比特甚至更多比特錯誤,這種情況下將無法采用EDAC功能進行數據糾錯,導致系 統錯誤操作甚至任務失敗。因此定時對RAM存儲單元進行更新是必要的,但在傳統EDAC電路 設計下,對RAM存儲單元的更新只能由計算機的CPU(單片機)進行,其操作流程如下:

(1) 從存儲單元讀出數據;

(2) 將讀出數據重寫入;

(3) 重復(1)~(2),直至全部單元更新完。

以航天計算機常用的80C32單片機為例,CPU對外部存儲單元的讀或寫操作需要2個指令 周期,讀完再寫入需要4個指令周期,每個指令周期包含12個時鐘。假設CPU時鐘為20MHz, 更新1M個RAM存儲單元需要的CPU時間為:4×12×1M 20MHz = 2.4s。

對于星上非常緊張的CPU資源來說,這是難以接受的,大大增加了星上CPU軟件的設計難 度。這種方法的另一個大的缺點是無法獲得數據錯誤信息,因為CPU直接讀取的是糾錯后的 數據,所以無法對星上SEU造成RAM單元出錯的概率和錯誤模式進行統計。

3.1 功能分析

由于FPGA的內部大量的邏輯資源,使EDAC電路設計可以實現更加復雜的功能。在星載計 算機中,為了提高效率并節省CPU資源,一個理想的EDAC電路設計,應具有以下三部分功能:

(1)數據讀寫功能。在CPU寫操作時,對原始數據進行編碼,生成校驗碼,并將原始數 據和校驗碼存儲;在CPU讀操作時,從存儲器中取出原始數據和校驗碼,進行計算,如有錯 誤,將錯誤糾正后輸出,如無錯誤,直接將原始數據輸出。

(2)自檢、自糾錯功能。在CPU控制要求下,可自動對所有EDAC保護的RAM存儲區進行 順序讀取和校驗,檢測出錯誤數據或校驗碼。在自檢狀態下,如果由CPU配置為自糾錯狀態, 當某一RAM單元檢測出單比特錯誤后,自動將正確數據和校驗碼重新寫入該RAM單元。該項功 能的實施,基本上可保證SEU對計算機RAM區造成的影響及時得到修復。

(3)錯誤信息處理功能。在CPU讀操作或者自檢狀態下,通過輸出錯誤標志信號,對CPU 產生中斷,對產生的錯誤進行相應處理。在CPU讀操作或者自檢狀態下,如果檢測出錯誤, 將出錯的地址、原始數據和校驗碼進行暫存,可由CPU讀取,進行相應處理。

3.2 設計與實現

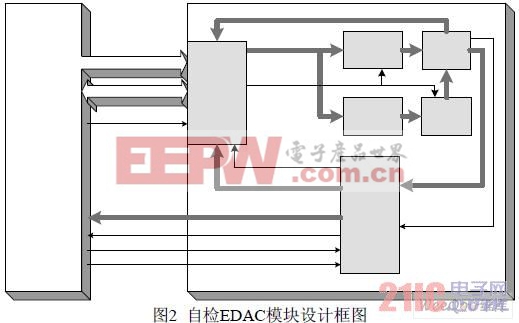

根據以上分析,筆者設計了如圖2所示的自檢EDAC電路,EDAC的功能主要由FPGA來實現。 到目前為止,具有航天等級的FPGA芯片已經具有內置的CPU硬核以及高達2.5Mbit的RAM資源, 因此該設計中的CPU和RAM模塊均可以是FPGA內部資源,當內部資源無法滿足設計要求時,也 可以采用外置CPU芯片或外置RAM芯片。

評論