基于FPGA的高精度時間數字轉換電路設計

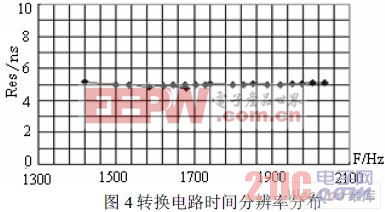

由該 TDC構成的脈寬測量電路在 Cyclone EP1C3Q240C8芯片實現,系統外部時鐘 25Mhz,PLL設置倍頻因子 8,由 SP1641B信號發生器提供固定的被測脈沖頻率 F,時間分辨率 Res的分布如圖 4所示,測試數據表明 Res在 4.9-5.1ns之間,理論值為 5ns。

測量和仿真數據表明該電路能達到納秒級時間分辨率,邏輯資源占用少,可在低密度芯片上實現作為專用測量電路使用,或在高密度芯片上作為功能模塊嵌入到特定功能的片上系統(SOC)中;該 TDC電路的轉換速度也在納秒級,使該電路適用于實時數據采集及高速數據處理系統。精度可調也是該設計一大特點,移位脈沖的工作頻率決定了該轉換系統的轉換精度,通過時鐘管理單元可以產生不同頻率的移位時鐘,從而測量精度可以根據具體需要進行適當調整。

3結束語

本基于 FPGA的時間數字轉換電路設計在占用較少芯片資源的前提下,實現了很高的測量精度,工作時數據轉換速度也在納秒級;本設計電路接口簡單可作為獨立的功能電路使用,亦可作為功能模塊 IP核[8]方便地嵌入到其他系統實現特定功能。基于 Altera芯片的時序仿真和硬件測試表明了該方法的可行性和準確性。

評論