基于FPGA的自定義總線MCMB的設計與實現

(1) SMC接口模塊

實現SMC總線到Wishbone總線的轉換,SMC總線至Wishbone總線接口轉換模塊如圖2所示。本文引用地址:http://www.j9360.com/article/189629.htm

該模塊的信號轉換可以分為以下三種:

1)數據地址線

地址線上將SMC總線的地址線SMC_A[15..0 ]譯碼成Wishbone地址總線ADR_O[15..0]。數據線上使SMC總線的輸入輸出復用數據線SMC_D轉換成兩個分開的單個輸入輸出信號DAT_O[15..0]和DAT_I[15..0]。

2)控制信號

當ARM發起SMC總線操作時,我們根據SMC總線操作的類型,譯碼得到以下輸出控制信號:WE_O、 CYC_O、 SEL_O[3..0]、 CTI_O[2..0]、STB_O和BTE_O[1..0]。

SMC總線的讀寫命令分別為NRD和NWE。當NWE為低時,表明當前操作是寫操作。NRD為低時,表明當前操作是瀆操作。Wishbone總線的WE_O信號只在寫操作時有效,所以當FSC0和NWE都有效時,便將WE_O信號置1,證明這是一個有效的寫操作,當FCS0有效但NEW為低時,為讀操作。

CYC_O有效表示Wishbone總線事務的開始。當ARM發起SMC總線操作時,可由SMC總線的FCS0信號譯碼得到。

SEL_O[3..0]代表Wishbone數據總線上的有效位。在系統的設計中將SEL_O[3..0]置全1,表明數據線上的每一位數據郜一直有效。

CTI_O[2..0]譯碼Wishbone總線的操作是單字操作和塊操作。選擇SMC總線地址線A[17]和A[18],A[17]定義為SMC_LAST;A[18]定義為SMC_BURST。這兩個信號用于對CTI_0 [2..0]的譯碼。當進行單字讀寫操作時,SMC_LAST和SMC_BURST均為低,CTI_O [2..0]譯碼為111;當進行塊讀寫操作并且不是最后一個數據相時,SMC_LAST為低,SMC_BURST為高,CTI_O[2..0]譯碼輸出010;當進行塊傳輸且為最后一個數據相時,SMC_LAST和SMC_BURST均置為高,CTI_O[2..0]譯碼輸出111,代表塊傳輸操作的結束。

3)響應信號譯碼

當外設和MCMB總線進入等待狀態時,需要產生NWAIT信號;當外設和MCMB總線狀態異常時,需要產生中斷信號。

Wishbone主模塊有三個輸入的響應信號,分別為ACK_I、ERR_I、RTY_I。當外設不能及時響應當前操作時,需要在SMC總線上插入等待周期。NWAIT是SMC總線的等待信號。當NWAIT為0時,ARM保持當前SMC總線操作,直到撤銷NWAIT為止。

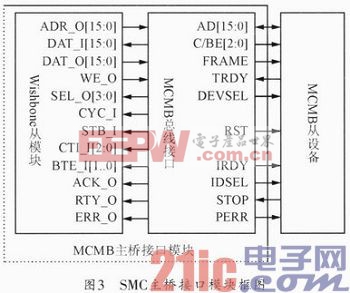

(2) SMC主橋接口模塊

實現Wishbone總線到MCMB總線的轉換,主要是對MCMB總線的各種狀態進行譯碼,并將譯碼結果與上面的Wishbone從模塊進行對接。模塊如圖3所示。

①數據地址

Wishbine從模塊的地址和數據的輸入輸出是分開的,但在MCMB總線上,地址和數據復用一個線,在這主橋中有個譯碼邏輯,將數據和地址進行轉換。即將ADR_O [15..0]、DATA_I [15..0]和DATA_O [15..0]譯碼為AD [15..0]。

評論