基于FPGA與有限狀態機的高精度測角系統的設計與實

3 系統設計與實現

3.1 軟硬件平臺

根據以上分析,編碼器輸出的原始信號經過有限狀態機處理后,得到了四倍頻的輸出信號。本系統采用FPGA實現四倍頻控制和計數功能,與用分立器件構成的倍頻計數電路相比,具有穩定度高,移植性靈活,可靠性好的特點。

硬件采用Altera公司的Cyclone系列FPGA芯片EP1C12Q240,編譯環境為Quartus II 5.1集成開發環境。在Quartus II的開發環境中,可以通過兩種方法來實現Mealy有限狀態機。第一采用硬件描述語言,第二通過Quartus II中的狀態機編輯工具來完成。本設計采用硬件描述語言來實現狀態機設計。

3.2 程序設計

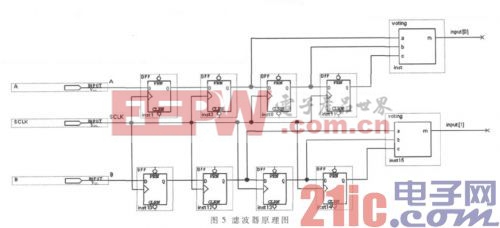

為了提高系統的實用性和穩定性,濾掉信號上的毛刺,在A、B相信號進入狀態機前,先設計一個濾波器進行初次濾波,每個信號用4個D觸發器和1個判決器來濾波;觸發器由時鐘SCLK驅動。小于一個SCLK時鐘周期的毛刺,都被濾波器濾掉了。濾波器的原理圖如圖5所示[6-7]。

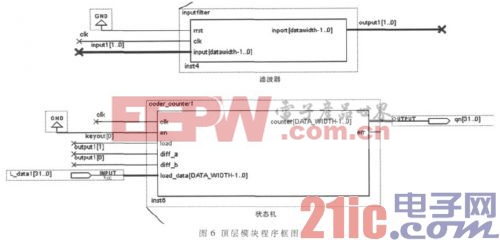

整個程序的設計是采用圖形和語言相結合的方法來實現的。頂層設計采用圖形文件,頂層模塊的結構圖如圖6所示。

內部的狀態機模塊采用VHDL語言來實現。頂層模塊包含兩個模塊,一個濾波器模塊,該模塊根據三選二判決的原理來濾掉毛刺;另一個模塊是狀態機模塊,最終輸出編碼器計數的結果。Input[0]和input[1]輸入引腳分別連接增量型編碼器A相和B相信號。q[31..0]為32位的計數器,輸出當前編碼器的計數值,dirout是編碼器的旋轉方向信號。

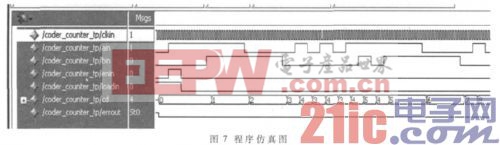

程序設計完成后,在仿真工具modelsim下進行波形仿真。仿真結果如圖7所示。從圖中看出,計數器能夠實現正向與反向計數,可以有效濾除脈沖上的抖動,獲得精確的計數值。

本文提出了一種基于有限狀態機的高精度測量系統,在FPGA上用有限狀態機實現了編碼器輸出脈沖的去抖,并通過32位計數器實現精確計數。最終在ARM處理器上完成角度的計算。通過大量反復試驗,試驗結果表明本文介紹的方法具有精度高、成本低、接口兼容性高、可靠性高、可移植性好等優點,可以有效抑制噪聲干擾,獲得高精度的角度數據。該方法已經成功應用在激光跟蹤測量系統中,該技術的推廣可以取得良好的經濟效益,具有重要實用意義。

fpga相關文章:fpga是什么

脈沖點火器相關文章:脈沖點火器原理

評論