如何選擇滿足FPGA設計需求的工藝?

FPGA 邏輯架構實際上是大量經過復制的定制設計邏輯單元(LE)陣列——微小SRAM,復用器和寄存器,以及交換結構,覆蓋了非常復雜的多層金屬。因此,可編程架構的設計是要在LE實現多少功能以及單元需要多少互聯之間達到很好的平衡。對于某一體系結構,架構的總密度對底層和中間金屬層的層距非常敏感。但是,由于規劃人員嘗試使用互聯堆疊下面所有的可用區域,因此,對于LE中晶體管的封裝密度也非常敏感。用戶在邏輯架構中實現的電路的速度和功效取決于晶體管特性,也與架構密度,互聯RC產品和晶體管驅動電流有關。

因此,一般而言,能夠提供較小金屬層距以及封裝更緊密的晶體管的工藝可以實現密度較高的邏輯架構,對于用戶電路,性能更好,功耗更低。泄漏電流是邏輯架構的一個特殊問題,這是因為,芯片設計人員并不知道用戶怎樣使用可編程邏輯,他們使用電路級功耗管理技術來降低基于單元的設計的靜態功耗,這種方法能力有限。

相反,基于單元的數字IP有關鍵通路,這些通路主要是通過本地短互聯或者底層金屬直接互相連接的快速晶體管。現代FPGA中的這一類結構包括數字信號處理(DSP)模塊、I/O和存儲器控制器、增強CPU內核,等等。這些IP模塊的大小主要受仔細封裝的標準單元庫的密度的影響,以及庫中各種單元的影響。在可編程架構中,用戶可以開發需要的任何電路,而基于單元的硬核IP是預先定義好的,因此,芯片設計人員可以采用所有的功耗管理技術。這樣,硬核數字IP將極大的受益于更小的工藝尺寸以及更高的晶體管速度,在系統層,可以使用功耗管理技術,調整平面FET較大的泄漏電流。

模塊RAM是一類特殊的基于單元的IP。一般使用代工線提供的,經過手動優化的SRAM單元進行開發,但是,FPGA設計人員通常會調整陣列,在模塊應用的范圍內,優化速度、密度和功耗。由于模塊非常靈活,因此,很難在FPGA RAM上實現功耗管理策略。FPGA中的其他結構可能不會對晶體管的所有特性變化敏感。

這些考慮意味著,某一系統應用FPGA的最佳工藝選擇取決于系統設計對可編程架構和基于單元的邏輯的相對壓力。對系統總體性能還有一定影響的是在架構中實現的模塊的行為,28nm或者20nm工藝中端FPGA能夠以較低的成本在較短的時間內實現所需要的系統性能。

最后,還有高性能模擬IP的問題,這些IP是目前鎖相環(PLL)和串化器解串器(SerDes)電路的主要構成。這些設計并沒有采用最小層距,相反,使用了各種尺寸的晶體管、電路布局和金屬層間距,這些通常涉及到了手動布局。它們對于晶體管的電氣行為非常敏感,包括,數字工程師不太關心的一些參數。數字設計人員仿真邏輯功能,模擬設計人員仿真晶體管。對于模擬設計人員,另一個絕對關鍵的問題是一致性:很多標準電路依靠密切匹配的成對的晶體管來實現。

在 finFET上還有一些爭論。某些模擬設計人員指出,您不能為FinFET選擇任意寬度。由于晶體管是豎立在側面,意味著是在縱向測量寬度,因此,它們必須有相同的寬度。您可以使用一個最小寬度的FinFET,或者,您希望電流更大,可以將幾個并聯起來使用。這些設計人員擔心,模擬設計人員很難甚至無法在其熟悉的電路拓撲中使用這些新晶體管。

但是,其他有經驗的模擬設計人員指出,更高的速度、更強的溝道控制,以及,特別是 FinFET更好的一致性,對于模擬設計都非常有利,遠遠抵消了晶體管寬度的量化問題。爭論還在繼續,而Intel在CPU中模擬結構上的工作表明,它們使用其22nm三柵極工藝開發了這一結構,三柵極晶體管極大的提高了高精度模擬設計的性能。

采用合適的工藝開始定制

工藝特性以不同的方式影響FPGA的不同結構。相似地,不同的應用對這些 FPGA結構有不同的要求。結果,在一定時期內,沒有一種工藝技術能夠為多種應用提供最合適的平臺。計劃、成本和性能要求促使FPGA中的某些結構采用混合定制方法來實現,以滿足FPGA設計對多種工藝選擇的要求。

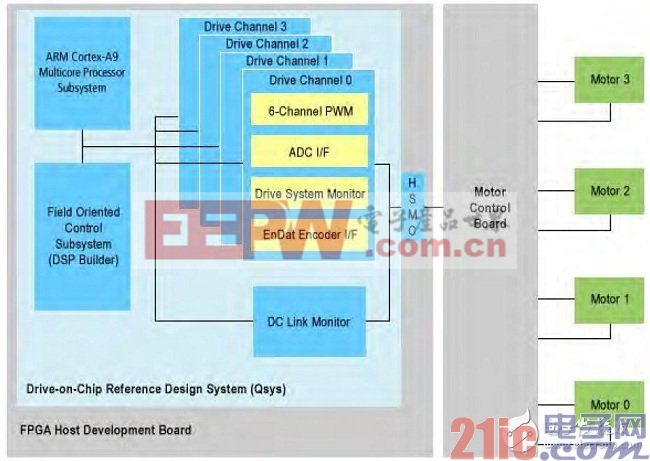

三個例子可以說明這一點。首先,考慮一個單芯片電機控制 SoC(圖3)。芯片接收來自四個電機的連桿傳感器位置數據,都是較高的kHz速率,以較低的MHz速率驅動四個驅動電路板。它連接至中速DDR2 DRAM,進行編碼和數據存儲,連接至工業以太網,將SoC連接至工廠車間控制網絡。

圖3.單芯片多軸電機控制器結合了基于單元的DSP電路來計算FOC算法,可編程邏輯對I/O信號進行編碼和解碼,CPU用于管理和功能安全算法。

芯片實際上支持兩項主要任務。第一項是在FPGA DSP模塊中進行計算的現場定位控制(FOC)算法,實際上是每一電機大量的矩陣算術。可編程架構中的I/O電路以相對較低的速率和功耗,對位置數據進行解碼,對信號進行編碼,以便驅動電路板。第二項任務是功能安全封裝,一組設計用于保護機器運行以及設備完整性的功能,運行在SoC FPGA的嵌入式ARM Cortex-A9 CPU上。

這一設計有兩個很大的難點。第一,客戶希望不斷提高能效和精度,降低噪聲,這些都要求更大的帶寬,更復雜的算法,進行FOC計算。因此,應用程序要求使用硬核DSP模塊和RAM。第二,成本問題,這個問題更嚴重。

對形勢進行分析,這一應用最關鍵的FPGA結構是硬核IP模塊、模塊RAM,以及隨著功能安全要求的提高,還有CPU內核。這些模塊相應地要求半導體工藝良好的標準單元庫,合適的SRAM以及盡可能低的價格。現在,Altera的Cyclone V SoC產品采用了TSMC的28低功耗(28LP)工藝,很好的結合了高性能硬核IP和存儲器,降低了成本,可以及時供貨。

幫助駕駛員開車

第二個例子是下一代汽車輔助駕駛系統(ADAS)設計。這一SoC接收來自汽車雷達和幾個HD視頻攝像機的數據,使用圖像處理例程和人工智能(AI)算法算出車輛的位置,驅動兩個實時顯示屏,向車輛控制模塊發送命令,進行換擋、剎車和傳動系統控制。大部分I/O數據流會通過一對冗余的10G以太網端口。由于嚴格的推出計劃,必須在2013年年中開始系統體系結構設計。

這一系統中的難點是進行大量的視頻和雷達信號處理,識別目標,滿足分類和AI例程的計算需求,以及大量的本地和外部寬帶存儲器的需求。這些需求主要依靠可編程架構來滿足,使用了DSP硬核IP、模塊RAM和外部 DRAM。由于計算負載是偶發的,車輛沒有移動或者慢速行駛時,計算很少,而計算強度基于環境的復雜度,因此,需要很好地進行功耗管理。這類FPGA需要金屬層距和晶體管性能優于目前中端FPGA的工藝,以便滿足可編程架構和硬核IP的性能目標。但是,設計最初并不需要FinFET那樣的速度和功耗。 Altera的20nm產品系列基于TSMC的20nm芯片系統(20SoC)平面工藝,很好的同時實現了帶寬、計算性能和可用性。

最后,讓我們進一步了解一下近期會怎樣。新一代數據中心將不僅僅包括高密度服務器類CPU芯片簇,而且還有大容量的高速FPGA。這些FPGA以及CPU和共享高速緩存將位于超高速本地網中,用作虛擬的動態重新配置網絡數據包引擎和計算加速器。

這類芯片要求很高的晶體管密度和金屬層距,提高芯片的容量和帶寬,特別是,考慮到服務器機架嚴格的散熱和功耗限制以及較高的占空比,這些都限制了動態功耗管理的效率,因此,功耗性能點超出了任何建議的平面晶體管的能力范圍。此外,為能夠連接超高速數據網絡,以支持外部存儲器極大的帶寬,這些FPGA需要的集成模擬電路性能水平超出了目前針對FPGA所討論的電路性能。這些應用促使Altera選擇了Intel的14nm三柵極工藝。

結論

本文介紹了三種場景,每一種都結合了硬核IP應用、可編程架構應用、存儲器帶寬,以及I/O帶寬,很好地滿足了不同半導體工藝的要求。這一工藝實際上就是 Altera的定制方法:每一類應用的FPGA性能、余量、計劃和成本都能夠滿足系統要求。最好的選擇給系統開發人員帶來了明顯的優勢。

評論