如何用FPGA構建便攜式超聲系統?

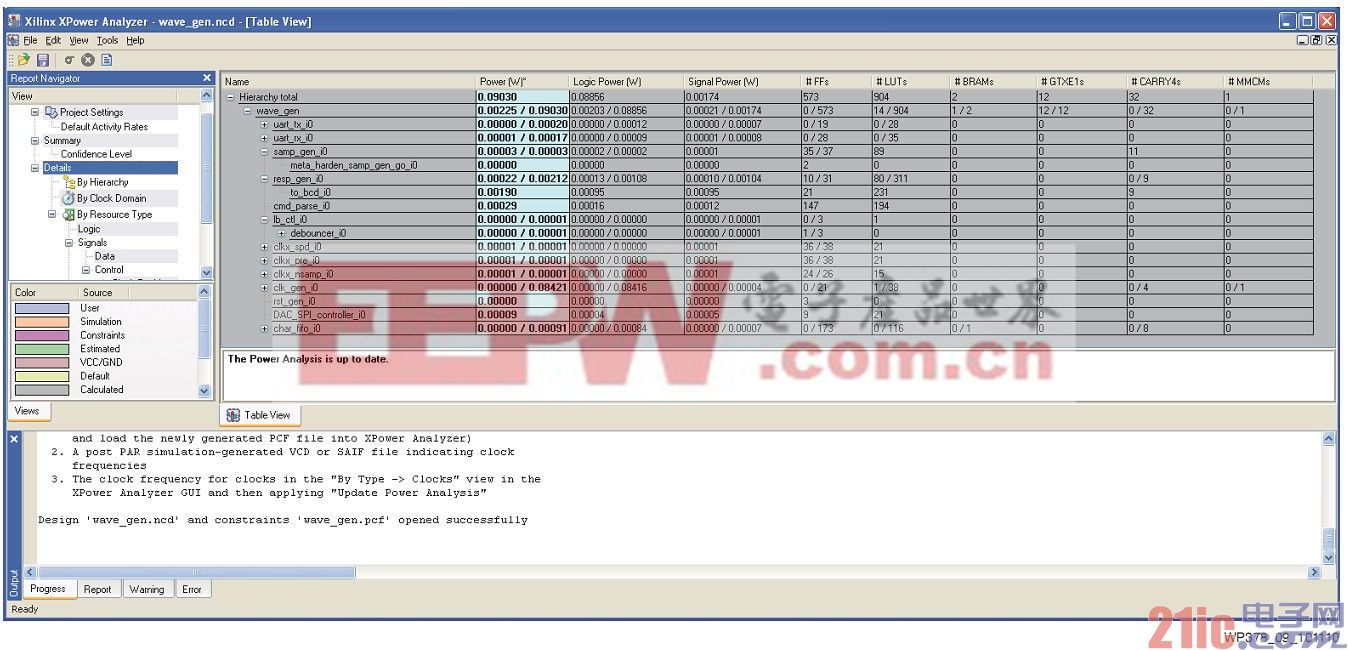

賽靈思獨特的自動時鐘門控技術能將動態功耗降低多達30%。下一步重要工作就是用賽靈思的XPower Analyzer全面分析設計功耗情況,如圖9所示。

圖9 XPower Power分析界面

該工具可提供準確的實現后功耗分析,凸顯了潛在能夠降低功耗的設計區域。根據功耗瓶頸情況,用戶能夠實現賽靈思自動化功耗改進工具的任意組合,如邏輯再綜合、功耗優化放置以及路由電容優化等。如果仍需要進一步降低功耗,我們還能用XPower工具來明確哪些模塊產生的功耗最多,哪些設計方法最適用于降低動態功耗。

采用賽靈思FPGA從容應對接口挑戰

便攜式超聲系統中最關鍵的接口瓶頸是AFE到波束形成器的接口,我們在此需要大量I/O與并行DAC和LVDSADC接口相連。

為了進一步降低AFE到波束形成器接口的復雜性,模擬供應商采用高速串行JEDEC JESD204A標準作為從ADC向DAC傳輸數據的高效途徑,其速率可高達每通道每秒3.125Gb。賽靈思能夠為采用GTP/GTX收發器的ESD204A標準提供全方位的支持。

雖然JESD204A標準是比較受青睞的解決方案,但在多個低邏輯密度的高引腳數FPGA上對前端設計進行分區更合適。這種方案幾乎徹底杜絕了在以下方面同時進行輸出(SSO)轉換的問題,如:在更多VCC/GND對上分布I/O;為PCB布局工程師提供更大的工作面積(這可進一步避免PCB路由擁堵問題),以及;為在更大的封裝和PCB空間(可作為散熱片發揮作用)中進行布局設計減少了散熱管理問題。不過,設計分區也會帶來PCB尺寸放大的不利影響,進而導致系統體積增大,因此設計人員應當根據空間約束、通道數量以及模擬前端的設計要求實現良好的平衡。

在此情況下,FPGA可謂最佳解決方案,能實現較多的引腳數量,同時還具有大容量的片上存儲器。

可高度擴展的設計

如果采用7系列FPGA的統一架構,就能大幅縮短開發時間,確保用戶快速在整個產品系列中實現設計模塊的移植。此外,IP核的可用性也能顯著獲得提升,因為賽靈思和IP核合作伙伴僅需一次性優化IP核即可,隨后就能根據不同的器件要求加以調整,從而盡可能減少修改幅度,而且每個系列的重復驗證也會很方便。統一架構的另一優勢在于其能在較短的時間內為新的超生系統獲得醫療設備認證,因為大部分HDL代碼都能在不同產品系列上實現重復利用,在某些情況下甚至包括網表的重復利用。

總而言之,賽靈思的通用架構能大幅提高超聲系統供應商的規模經濟效益,幫助他們提供多種不同的系統功能和復雜性選擇,同時還能縮短開發時間和產品的批準認證時間,使供應商能夠更方便地根據不同應用需求使用性價比最高的器件。

賽靈思IP核

賽靈思IP核是賽靈思設計方案的關鍵構建塊。種類豐富的基礎IP核可滿足FPGA設計人員的一般性需求,而穩健可靠的特定領域和特定市場IP核則能滿足DSP、嵌入式和連接設計的特定需求。超聲系統所需的眾多關鍵DSP功能和連接接口都可作為賽靈思或合作伙伴的IP核提供。使用賽靈思IP核不僅能夠最大限度地縮短開發時間,并且還能幫助用戶集中精力實現產品差異化設計,而非標準功能開發——這是使用賽靈思產品的一項獨到的優勢。

總結

Spartan-6、Virtex-6和7系列FPGA均可提供專用ASIC和DSP的高性能,同時還具備極低NRE成本、大幅縮短產品上市時間、便于設計移植、高I/O數量和PCB布局簡化等優勢。此外,配合業界領先的功耗優化工具,賽靈思的40nm和即將推出的28nmFPGA定制低功耗工藝技術還能大幅降低功耗,顯著優于業界同類型的競爭解決方案。上述所有優勢都能幫助便攜式超聲系統開發人員快速部署系統,在預算和功耗要求限度內推出最新技術,從而改進患者的護理工作。

fpga相關文章:fpga是什么

模數轉換器相關文章:模數轉換器工作原理

評論