基于FPGA的實時視頻信號處理平臺的設計

2.2 存儲控制模塊

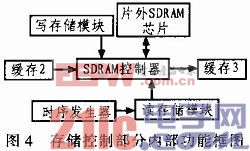

存儲控制部分內部功能模塊如圖4所示。本文引用地址:http://www.j9360.com/article/189535.htm

寫SDRAM存儲模塊判斷緩存FIFO中的RGB信號即像素點數據長度滿足720個時,向SDRAM控制器發出啟動存儲請求,然后SDRAM控制器從緩存FIFO中依次讀取數據存入片外的SDRAM中,存576次后即為一幀圖像的數據,在SDRAM的2個Bank中各存入一幀圖像數據,采用乒乓存儲機制進行對幀數據的讀出操作。由于采集到的圖像幀頻為25 Hz,要提高到VGA顯示的刷新頻率60 Hz,因此時序發生器要控制讀SDRAM存儲模塊對SDRAM的幀數據進行讀出,平均每幀圖像數據要讀取的次數為2.4次,規定每5幀為一次循環,這5幀數據共讀取12次,比例為2:3:2:3:2,同時,每幀的數據分576行次讀出打入緩存FIFO,但每次均寫入3行,此處是為后級幀放大做準備,只要FIFO中的數據為空時,就立刻打入幀圖像的下3行數據。SDRAM控制器模塊設計如圖5所示。

2.3 VGA顯示控制模塊

VGA顯示控制部分內部功能模塊如圖6所示。

VGA顯示控制模塊主要是產生滿足分辨率為1 024x768的行頻和場頻,因此還要對720x576的分辨率進行放大,采用的方法是選擇2個互質的整數m和n,使其比值m/n與給定的放大比例盡可能接近。720x7≈1 024x5,576x4≈768x3,因此水平方向的5個原始像素點放大為7個新像素點,垂直方向的3個原始像素點放大為4個新像素點,所以前一級每次存入緩存有3行數據,水平和垂直方向上的像素放大函數如下所示。

fpga相關文章:fpga是什么

評論