數字可編程增益放大器應用發(fā)散指數曲線

DPGA(數字可編程增益放大器)是一種實用的信號處理元件,在模數轉換器必須獲取廣泛動態(tài)范圍內的信號時應用。如果不能容納輸入信號振幅以便匹配和有效地利用模數轉換器跨度,低輸入可能不能以足夠的分辨率數字化,高輸入可能會超出模數轉化器額定的界限,并且完全丟失。

本文引用地址:http://www.j9360.com/article/188918.htm

現有的DPGA設計通常將一個乘法數模轉換器并入一個運算放大器的反饋回路中,從而使乘法數模轉換器的輸入代碼確定放大器的閉環(huán)增益。現有的幾種單片電路DPGA使用這種拓撲,如凌力爾特的LTC6910和美國國家半導體的LMP8100。 但是,DPGA的數字增益控制位有時不方便提供,而且這些設備的輸出跨度可能不足,例如,不足以對接±10V模數轉換器輸入跨度。 此外,這些設備的可用增益設置的分辨率通常很不精確,例如,每步增益2:1(2-to-1),這些設備的功耗有時很大。與之相反,本設計實例介紹一種采用發(fā)散指數曲線理念的新型DPGA。

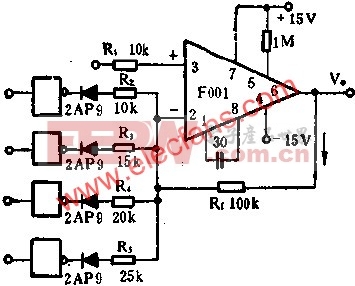

最簡單或設計者最為熟知的波形莫過于e-t/RC收斂指數,即,將一個起初充電到輸入電壓VIN的初級RC電路漸進放電到零,其中,當t=T=loge(2)RC時V=VIN/2,當t=2T時V=VIN/4,當t=3T時V=VIN/8,依此類推。設計者可能不太熟悉但依然簡單的波形是,用合成一個負電阻的有源電路代替R時(圖1)的同一RC拓撲。使用-R取代R,以便使RC時間常數為負:-RC和波形函數生成發(fā)散指數VIN×e+t/RC。之后,波形并沒有收斂到零,而是在理論上發(fā)散至無窮大。當t=T時V=2VIN,當t=2T時V=4VIN,當t=3T時V=8VIN,依此類推。因此,不管輸入電壓有多低,只須在啟動負放電之后等待t=log2(V/VIN)T。

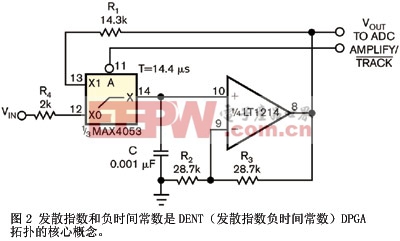

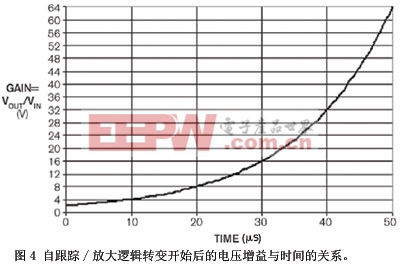

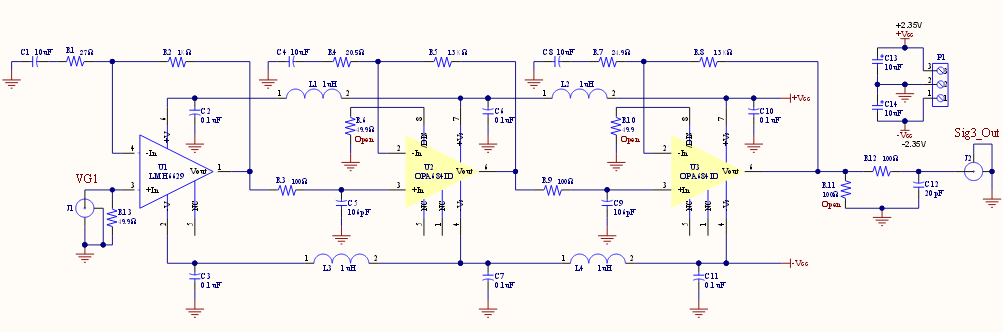

發(fā)散指數和負時間常數是DENT(發(fā)散指數負時間常數)DPGA拓撲(圖2)的核心理念。 當AMPLIFY/TRACK(放大/跟蹤)控制位轉向邏輯“1”時,運算放大器跟隨器的兩個時間反向增益生成一個負時間常數:-(R+1RON)(C+CSTRAY)=-14.4ms,其中,RON是CMOS開關的導通電阻,CSTRAY是C(圖3)周圍的寄生電容。它還會生成一個發(fā)散指數:VOUT(t)=VIN×2(t/10ms+1)。由此,增益是2(t/10ms+1)。放大控制位的1ms時間分辨率提供1.07:1=0.6 dB=33步/十進增益編程分辨率。圖4顯示自跟蹤/放大邏輯轉變開始后的電壓增益與時間的關系。

評論