基于TMS320C6416T的數據采集存儲系統設計

隨著數字信號處理技術的飛速發展,模數轉換作為數字信號處理的前端,其重要作用日益凸顯。采用DSP器件TMS320C6416T,結合A/D轉換器THSl2082和SDRAMHY57V283220T實現高速通用數據采集存儲系統,該系統可為數字信號處理提供數字化前端,充分發揮高性能DSP在數字信號處理上的優勢,廣泛應用于雷達、通信等領域。

2 器件簡介

2.1 TMS320C6416T簡介

TMS320C6416T型DSP工作主頻高達1 GHz,處理性能可達8 000 MI/s,片上存儲器采用兩級存儲器結構,第一級存儲器包括相互獨立的程序和數據,只能用于CPU高速緩存訪問;第二級存儲器尋址空間為1 M字節,可以選擇配置為SRAM或2級Cache。片內資源主要含有增強型直接存儲器訪問(EDMA)控制器、外部存儲器接口(EMIF)、主機接口(HPI)、通用目標輸入輸出(GPI0)、多通道緩沖串行接口(McBSP)、中斷選擇器、定時器、節電邏輯等。

2.2 THSl2082簡介

THSl2082是TI公司的可編程、雙通道、低功耗、內置FIF0的8 MS/s采樣速率的12位并行高速A/D轉換器,可與DSP實現無縫鏈接。THSl2082含有兩路采樣保持器,可同時對兩路信號采樣保持,并按順序轉換各通道的采樣保持值。單通道最高采樣頻率可達8 MS/s。而同時采樣兩通道的模擬信號,其采樣頻率為4 MS/s。THSl2082內部功能框圖如圖1所示。

THSl2082內置2個控制寄存器(CRl和CR0),通過向內部控制寄存器寫入特定的控制命令設定該器件的具體工作狀態。輸入引腳Dll/RAl和Dl0/RA0可作為內部控制寄存器的地址線,并用于選擇控制寄存器CRO或CRl。內置16字FIF0可編程設定采集多次數據后南DATA_AV信號線中斷CPU讀取數據,減少CPU讀取數據的巾斷次數,提高系統的實時性。THSl2082可采用內部電壓和外部電壓供電,并由內部寄存器控制。

3 系統硬件設計

3.1 數據采集電路設計

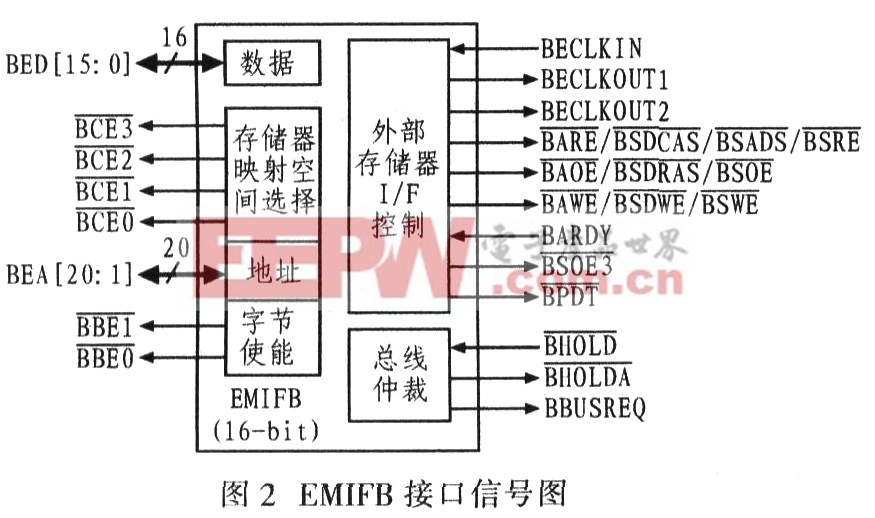

TMS320C6416T的外部存儲器接口(EMIFA、EMIFB)可與外部元件無縫鏈接,片外設備(存儲器或I/O)則通過外部存儲器接口(EMIF)進行訪問。其中EMIFB為16位存儲器總線,分成4個空間,即BCEO~BCE3,每個存儲空間可獨立配置。本系統設計采用EMIFB的BCE2存儲空間,最高工作頻率為133 MHz,工作時鐘來源為BECLKIN(外部輸入時鐘)、CPU時鐘四分頻(250 MHz)、CPU時鐘六分頻(167 MHz)。EMIFB接口信號如圖2所示,其中BECLKOUTl時鐘輸出和EMIFB輸入時鐘的頻率相同。BECLKOUT2輸出時鐘的頻率為EMIFB輸入時鐘頻率的1/2或114。BED[15:0]為16位數據總線,BEA[20:1]為20位外部地址總線。

評論