基于DDS技術的BPSK信號生成

0 引言

本文引用地址:http://www.j9360.com/article/188869.htm直接數字式頻率合成器(Direct Digitalfrequency Synthesizer,DDS)是從相位概念出發,直接合成所需波形的頻率合成技術。VHDL是IEEE的工業標準硬件描述語言,可描述硬件電路的功能、信號連接關系及定時關系,在電子工程領域用來描述、驗證和設計電子線路,得到了廣泛應用。故將VHDL語言與DDS技術結合,設計生成BPSK信號。

1 DDS的基本原理

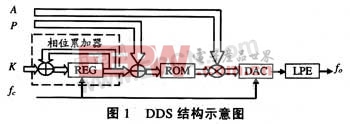

DDS把一系列數字量形式的信號通過數模轉換器(DAC)轉換成模擬量形式的信號,其基本結構如圖1。

DDS由相位累加器、加法器、波形存儲器(ROM)、數字乘法器、D/A轉換器和低通濾波器(LPF)組成。DDS的核心是相位累加器,由一個加法器和一個相位寄存器(REG)級聯構成。在參考時鐘fc的控制下,相位累加器對頻率控制字K進行線性累加,輸出的和再與相位控制字P相加后作為地址,對ROM尋址。ROM中存放經過采樣、量化處理后的周期性連續信號一個周期波形的幅度值,即與一個周期的相位采樣相對應的函數波形查找表,不同相位地址對應周期信號的不同幅度值編碼。ROM輸出的幅度值編碼通過數字乘法器被幅度控制字A加權,加權后的幅度值編碼經D/A轉換器變成階梯波,再經低通濾波器平滑后就可得所合成信號的模擬波形。合成的信號波形取決于ROM中存放的幅度值數據,故用DDS可產生任意波形。

設相位累加器的字長為N,則DDS的輸出頻率f0和頻率分辨率(即最小輸出頻率)△fmin分別為:

只要N足夠大,DDS可以得到很小的頻率分辨率。要改變DDS的輸出頻率,只要改變頻率控制字K即可。

根據Nyquist采樣定理,在對連續信號進行采樣的一個周期內,采樣頻率不能改變,故利用DDS進行信號合成時,在信號合成的一個周期內,頻率控制字K不能發生變化,也就是K在每次改變之前至少應該持續2N/K個DDS時鐘周期,即2N/K/fc。

通過改變相位控制字P,可以控制輸出信號的相位參數。設相位加法器的字長為M,當相位控制字由0變到P(P≠0)時,ROM的輸入為相位累加器的輸出與相位控制字P之和,因此,其輸出的幅度值相位會增加2πP/2M,從而使最后輸出的模擬信號產生相移。

DDS輸出信號的幅度可以通過在ROM之后加入一個數字乘法器來實現。幅度控制字A起到對ROM所輸出的幅度值編碼進行加權的作用。

可見,當DDS的相位累加器字長和相位加法器字長確定后,通過改變K、P、A就可以有效地控制DDS輸出的模擬信號的頻率、相位和幅度,這就是DDS技術的調制特性。

2 采用VHDL語言實現DDS

為簡單起見,以下所描述的DDS僅設置了頻率控制字K,相位控制字P和幅度控制字A都未予以考慮,其處理可類推。DDS的輸出為正弦波信號。

由于正弦波關于π奇對稱,關于π/2與3π/2偶對稱,因此波形存儲器(ROM)中只需存儲其1/4個周期的幅度值編碼。具體地,ROM中存儲正弦波0~π/2相位范圍內的256個采樣點的幅度值,采用8位編碼。而DDS的輸出為9位,最高位作為符號位,用以區分幅度值的正負,“0”表示正,“1”表示負。ROM為8位地址尋址,而相位累加器的字長采用10位。最高位用以區分正弦波的前、后半周期,“0”為前半周期,幅度值為正,“1”為后半周期,幅度值為負。次高位用以區分正弦波前、后半周期的前、后1/4周期,“0”為前1/4周期,尋址地址為相位累加器的低8位,“1”為后1/4周期,尋址地址為相位累加器低8位的取反。

用VHDL實現DDS的源程序的核心部分如下:

在Xilinx ISE 8.2i開發環境中對其進行仿真的結果如圖2。

評論