高速串行數據收發器CY7B923/933及應用

MODE=H,收發送器工作于直傳模式,即收發送器直接傳輸數據不編碼,編碼和解碼由外部協議控制器完成。輸入分成10位,數據需預先編碼,編碼方式任意,但需保證有足夠的躍變密度(每10位至少一次),使接收器鎖相環能正確鎖定相位,且編碼需與傳輸介質兼容。

無論是編碼模式還是直傳模式,若處于空閑狀態(時鐘CKW上升沿時ENA=ENN=H),編碼器將自動插入同步字K28.5(即C5.0)以保證接收器與發送器處在同步狀態。

2.3 自檢模式

BISTEL =1,收發送器工作于自檢模式,7B923可分別發送兩種信號來檢測整個通信鏈路是否正常:一種是1與0相間的連續信號;另一種是循環發送的偽隨機序列信號。若為后者,7B923輸入寄存器轉換成線性反饋移位寄存器LFSR,它可產生一組511個字節的偽隨機代碼序列,包括了所有的數據字和專用字。 7B933將輸出寄存器也變成LFSR,產生與發送器相同的偽隨機代碼序列,并與接收的序列相比較。若相同,則整個通信系統工作正常,否則為異常,使 RVS=H給出錯誤信號。每次循環,7B923的RP及7B933的RDY都將輸出一脈沖,此脈沖可用于記錄循環次數以控制自檢時間。7B923還可發送違規信號,以檢測報錯系統是否正常。這些信號都大大方便了故障診斷。

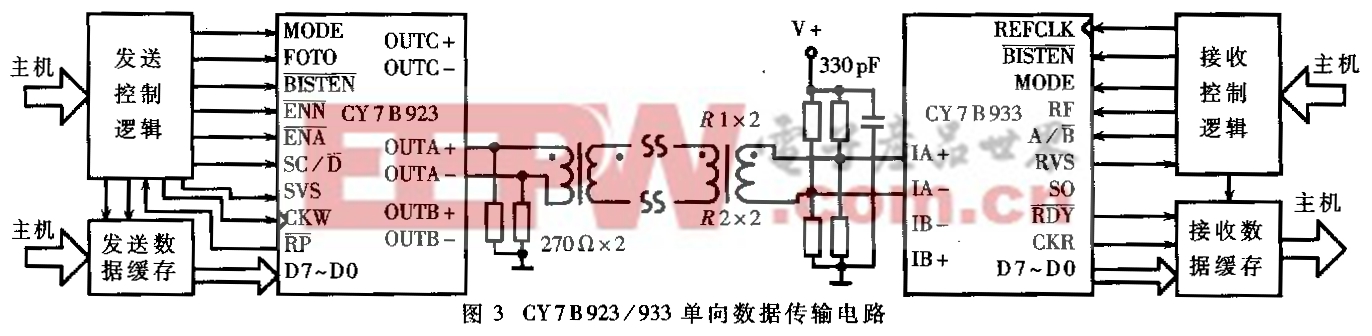

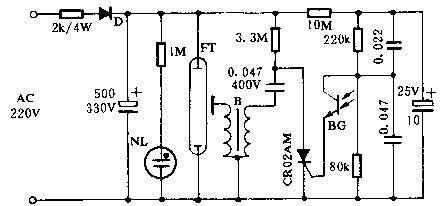

圖3 為采用CY7B923/933實現的單向數據傳輸的應用電路。主機發送控制命令,通過控制邏輯控制CY7B923/933工作在傳輸或自檢模式。這里控制邏輯用FPGA實現,也可采用其它數據邏輯器件實現。控制電路應包含RP、RVS端的檢測,以判斷系統工作正常與否,及時進行錯誤處理。主機數據傳輸速度一般與CY7B923/933不一致,發送端及接收端都需設置數據緩存,緩存一般用FIFO,我們采用CYPRESS公司的CY7C45系列,它可與 CY7B923/933組成無縫接口。若用FIFO的標志位作控制信號,則應注意標志延遲時間。CY87B933的輸出信號CKR,可作為其輸出數據寫入 FIFO垢時鐘,RDY可作寫FIFO使能信號,使用RDY的優點是同步字串到它無效,自動濾除同步字串,這就保證了只將有獎懲數據寫入FIFO,避免同步字將FIFO填滿。電路板設計應采用四層板,CFY7B923/933的位置應靠近雙絞線接口使連線最短,連線長度應盡量保持對稱。輸出輸入端都應接匹配電阻,如圖3所示。R1、R2阻值由下式給出:R1=(VccRt)/Vtt;R2=(VccRt)/(Vcc-Ctt)。式中,Rt為傳輸線阻抗;Vtt=Vcc-2V。Vcc=5V,UTP雙絞線阻抗為100Ω,則R1=183Ω,R2=275Ω。

作者在一VME總線長距離高速點對點串行通信系統中,采用最大數據傳輸率為330Mbps的標準CY7B923/933ey UTP雙絞線,實現了400Mbps的串行數據傳輸,工作穩定可靠,誤碼率小于10 -10。該工作是在中科院高物理研究所過雅南研究員、趙棣新研究員的指導下完成的,在此表示衷心地感謝!

評論