Cache結構的低功耗可重構技術研究

隨著集成電路的工作速度和芯片集成度不斷提高,芯片的功耗問題變得越來越突出,高性能低功耗設計已經成為當前集成電路領域的一個重要課題。在以微處理器為核心部件的VLS1系統中,Cache是系統取得高數據傳輸率的關鍵部件。在現代CPU中,Cache的功耗約占處理器總功耗的30%~60%,有效降低這部分的功耗,對芯片的低功耗設計有著重大的意義。

1 Cache低功耗相關研究

Cache平均訪問功耗是Cache性能表現的一個重要因素。Cache平均訪問功耗由Cache命中時的訪問功耗、失效時的訪問功耗和失效率三者決定。失效時的訪問功耗又包括兩部分:一部分是Cache失效時Cache電路的功耗,另一部分則是下一級存儲系統的訪問功耗。因此降低Cache功耗可以從三個方面考慮:一是降低Cache的失效率,二是降低Cache訪問能量,三是降低主存訪問能量。

為了達到低功耗的目的,對Cache結構做了一些改進:Phase―lookup Cache結構,應用兩級查詢的機制,即先訪問tag array,只有命中的那一路data才會在第二相去訪問,這樣就降低了組相聯Cache中數據array部分的功耗,但增加了Cache訪問的時間;Way predictive組相聯Cache結構,在默認情況下只訪問一個tag array和一個data array,只有在默認訪問失效時才會去訪問其他的tag和data array,這種方法也以增加Cache訪問時間的代價來換取低功耗;偽組相聯Cache結構,是具有多個命中時間的Cache結構,Cache中的每一路可以被順序讀取,從而可以比傳統的同時讀取結構節省一部分功耗;另外還有基于壓縮方法方面的研究,針對高頻值的局部性,在讀寫Cache的過程中,對高頻出現的數據值進行壓縮存儲,用較少存儲空間保存編碼后的數據,在一定程度上減少了Cache的訪問功耗。

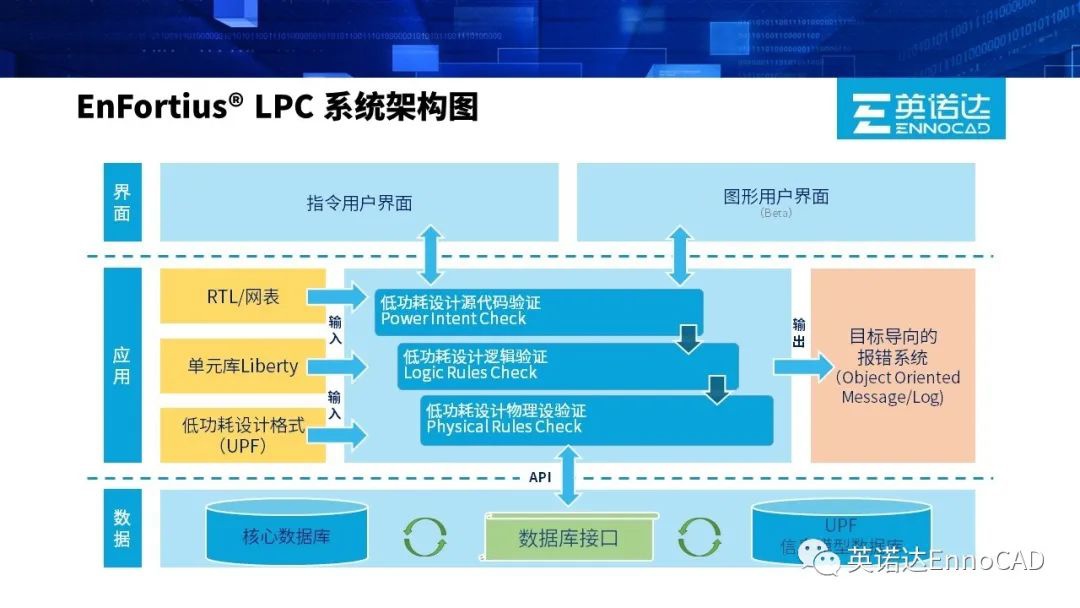

低功耗可重構的Cache研究在最近幾年得到關注,通過改變Cache的結構參數,不管是用硬件實現還是用軟件實現,針對不同的程序來配置優化的Cache結構,盡可能地關閉不使用的Cache,兼顧了系統的性能和功耗。Cache的結構參數很多,主要的參數有容量大小、相聯度、塊大小、替換算法、寫回策略等。一般而言,系統中的Cache替換算法和寫策略是固定的,如果改變也可以在軟件層面上實現。所以主要關注Cache的硬件結構是否可重構,僅研究其中幾個參數(如Cache容量、塊大小和相聯度)對訪問功耗的影響。在設計芯片之前可以使用CAD工具來確定對命中時間和功耗的影響。CACTI程序是一個可以評估CMOS微處理器各種Cache結構訪問時間和功耗的CAD工具。對于一個給定的最小特征值,可以改變Cache容量、相聯度和讀/寫端口的數目,以估計各種情況的Cache命中時間和功耗。可重構Cache結構需要綜合考慮Cache的命中率、平均訪問時間和訪問能量等性能,合理選擇Cache的配置參數。

2 可重構Cache的體系結構

要實現可重構Cache,首先Cache的結構要支持運行過程中的動態劃分,其次要有檢測Cache命中率的硬件或者軟件機制,并且有相應的動態配置算法。

2.1 可重構Cache系統設計

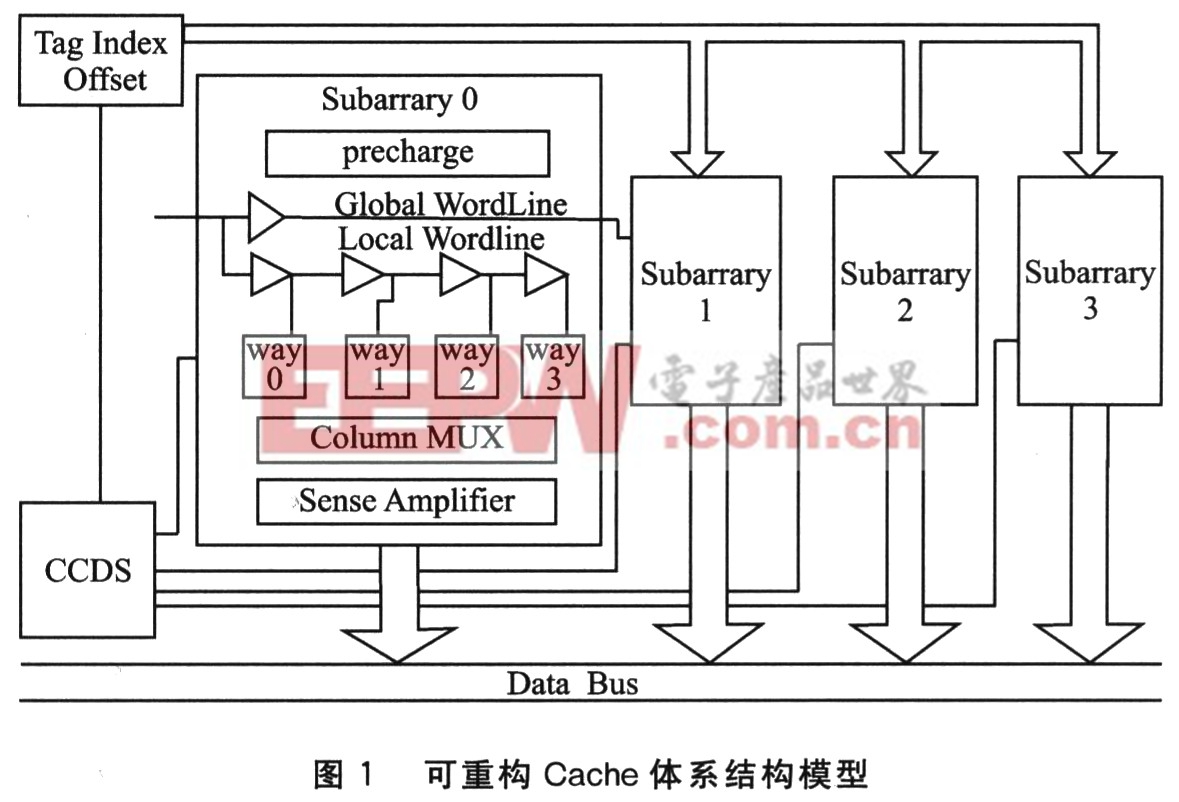

文獻提出了一種可重構的數據Cache結構。該Cache的數據區被平均分為4個子分區(subarray),每個子分區又分為4組。在Cache訪問時,只有一個子分區打開,其他子分區的線路不被激活,從而節省了功耗。圖1給出了整個Cache體系結構及功能模塊。

與傳統Cache結構相比,圖1中增加了Cache配置動態選擇器(Cache Configuration Dynamic Selector, CCDS),CCDS用來更新內部狀態機,并決定合適的Cache配置。通過配置CCDS,可以使整個子陣列無效,或者使有效子陣列中的某些路無效。對于無效的子陣列或者路,局部自選線(Local Word Line)、預充電(Precharge)和讀出放大器(Sense Amplifier)都無激勵。通過這些改進使得傳統的固定劃分的Cache具備了動態配置能力。

改進后的Cache外在表現為一個虛擬的兩級Cache:Ll/L2。這種分級方式同傳統的L1/L2兩級Cache結構不同,L1 Cache由激活的不同子分區以及子分區內不同的路數構成,未激活的部分為L2,在L1未命中時激活以進行訪問,L1和L2在物理實現上表現為同一級。Cache的地址劃分仍為三部分:標志位、索引位和塊內地址。圖2給出了Cache的地址劃分情況,可分為塊地址(Block Address)和塊內偏移(Block offset)。塊地址可以進一步分為標志字段(Tag)和索引字段(Index)。其中Tag的后兩位SS用來做子分區的選擇位。訪問Cache時,首先訪問L1,當L1命中時就直接返回,只有在L1訪問失效時才會將所有數據區打開。對不同的應用程序,L1和L2大小的劃分不同,其訪閩時間和運行功耗也會有較大差異。

評論