基于DSP Builder的Chirp信號源設計

根據Chirp函數在頻域上的性質,可以得出輸入控制字與輸出頻率之間的對應關系有線性和非線性兩種:本文引用地址:http://www.j9360.com/article/188609.htm

![]()

首先采用DSP Builder庫中的單步增/減子模塊(Increment/Decrement Block)建立采樣點控制字產生單元。該模塊能按照階梯式規律步進逐一產生控制字信號,并保持一段時間在模塊設置項(Clock Phase Se-lection)中設置,當增減方向(Direction)設置為Incre-ment時得時域輸出,其表現如圖7所示。

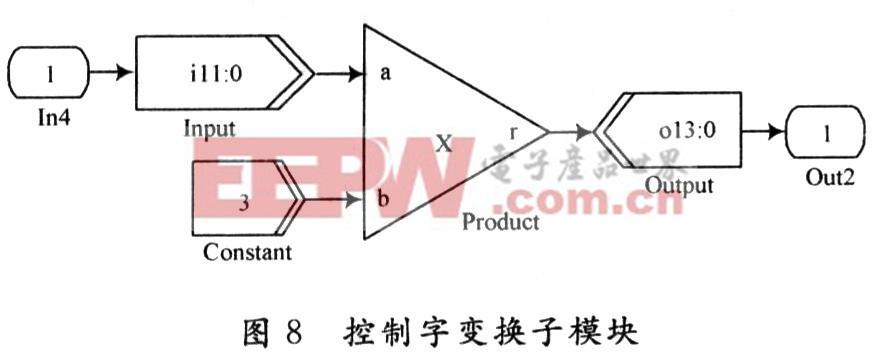

其次根據需要建立控制字變換模塊,即對Incre-ment/Decrement模塊輸出的采樣點控制字進行換算,轉化為DDS的頻率控制字。這需要根據不同Chirp函數的變化規律,例如:如果是線性頻率的輸出,則采樣點應該與輸出頻率有線性的函數對應關系;如果是非線性頻率的輸出,則采樣點應該與輸出頻率有非線性的函數對應關系。根據不同的傳輸函數建立該子模塊:

例如:fout=kn+f0。當k=3時,建立子模塊如圖8所示。

將上述模塊向上生成子模塊后,連接的整體仿真如圖9所示。

并在DDS的輸出端建立FFT觀測窗口。

4 驗證與仿真

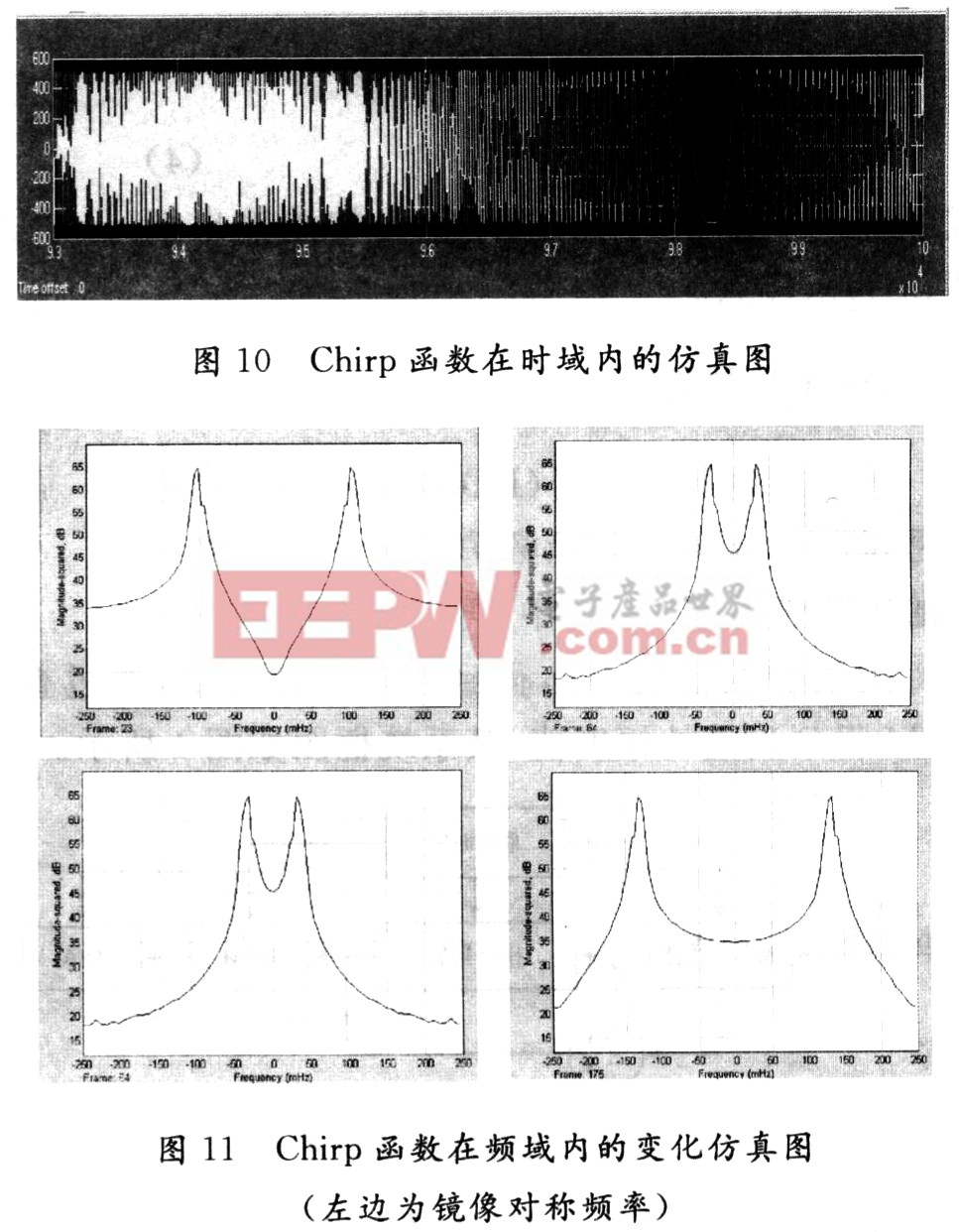

假設現在的初始相位為0,初始頻率也為0,采樣點步進控制字設置為輸出12為步進循環增加模式。在時域輸出觀測窗口(Scope)中觀察到圖形如圖10所示。

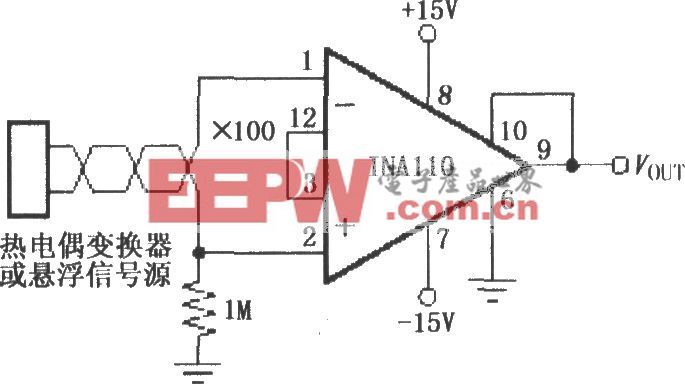

從圖11中可見,輸出信號的頻率發生了周期性并且有規律的變化,證明了該設計能很好地實現Chirp信號源的功能。并且通過Altera DSP Builder提供的SignalComplier工具,能很輕松地生成HDL(VHDL或者Verilog HDL)代碼下載到FPGA中運行,大大簡化了FPGA設計。

5 結 語

根據Chirp函數特定的輸入/輸出(線性和非線性)關系,計算得出當前輸入字與輸出頻率的對應關系,然后設計控制字子模塊產生DDS模塊的頻率控制字,驅動DDS產生不同的輸出頻率,通過在Matlab的Simu-link環境下的仿真驗證,得出不同時刻輸出的頻譜圖,驗證了該設計能很好地實現Chirp信號源。

評論