兩種高頻CMOS壓控振蕩器的設計與研究

鎖相環在通訊技術中具有重要的地位,在調制、解調、時鐘恢復、頻率合成中都扮演著不可替代的角色。可控振蕩器是鎖相環的核心部分。最近,鑒于對集成電路低功耗和高集成度的追求,越來越多的研究人員投人到基于CMOS工藝的壓控振蕩器的設計。環形壓控振蕩器因為具有寬的調諧范圍和小的芯片面積,在電路的精心設計下也可以具有不錯的相位噪聲性能,從而在數字通信系統中得到廣泛的應用。而隨著CMOS工藝特征尺寸的不斷減小,根據CMOS工藝按比例縮小理論,電源電壓也要同比例降低。與采用1.8 V電源電壓的0.18 μm CMOS工藝相比,傳統全差分延時單元結構的輸出信號的擺幅被限制在非常小的區域內,不但降低了輸出信號的信噪比(SNR),而且必須經過放大等一系列處理后才能送給下一級電路。文中分析了影響壓控振蕩器性能的重要參數,同時設計實現了兩種多諧壓控振蕩器,給出了相應的實驗結果。

本文引用地址:http://www.j9360.com/article/188458.htm

1 VCO的工作原理與性能指標

VCO是一個電壓/頻率轉換電路,在環路中作為被控振蕩器,它的輸出頻率應隨控制電壓線性地變化。一個理想的VCO其輸出頻率和輸入頻率的關系

ωout=ω0+KVCOVcont (1)

式中,ω0是控制電壓Vcont為零時的振蕩器的固定頻率,KVCO為VCO的增益或靈敏度(單位為rad/s?V-1)。

由式(1)可以推導出VCO的傳輸函數

由式(2)可以得出,當VCO被放在鎖相環中時,其輸出經分頻器后接到鑒相器的輸入,對鑒相器輸出起作用的不是其頻率,而是相位。所以在鎖相環中VCO通常被看作輸入為控制電壓,輸出為相位的系統。

所以VCO在鎖相環系統中就像一個理想的積分器,其傳輸函數可以表示為

在實際應用中,VCO的線性范圍有限,超出這個范圍之后,環路的參數就會變化較大,不利于環路設計。通常,評價VCO的好壞主要有以下特征:

(1)低抖動或低相位噪聲:由于電路結構、電源噪聲、地噪聲等因素的影響,VCO的輸出信號并不是理想的方波或正弦波,其輸出信號存在一定的抖動,轉換成頻域后可看出信號中心頻率附近也會有較大的能量分布,即相位噪聲。VCO輸出信號的抖動直接影響其他電路的設計,通常希望VCO抖動越小越好;

(2)寬鎖定范圍:VCO的調節范圍直接影響鎖相環的調節范圍,通常隨著工藝偏差、溫度以及電源電壓的變化,VCO的鎖定范圍也會隨著變化,因此要求VCO有足夠寬的調節范圍來保證VCO的輸出頻率能夠滿足設計的要求;

(3)穩定的增益:VCO的電壓一頻率非線性是產生噪聲的主要原因之一,同時,這種非線性也會給電路設計帶來不確定性,變化的VCO增益會影響環路參數,從而影響鎖相環的穩定性。因此,希望VCO的增益變化越小越好。

2 VCO的設計

環形振蕩器是常見的振蕩器類型,它由若干增益級電路及聯組成。一般它的振蕩頻率很高,而且結構簡單易于實現。基本組成單元可以是反相器或差分對。

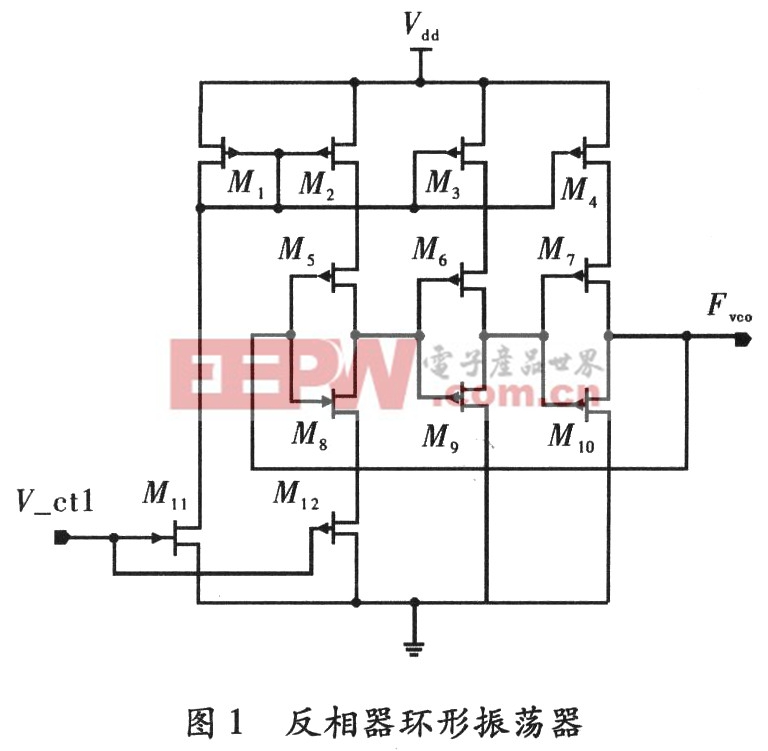

2.1 反相器環形VCO設計

單級的反相器只能提供180°的相差,為了滿足相位條件,最簡單的環形振蕩器應當至少由3個反相器串聯組成。隨著振幅的不斷增大,各級電路會經歷非線性,而達到飽和狀態,此時振幅和頻率都處于穩定狀態。用大信號分析其振蕩周期,假設每級反相器的延遲時間都是T,通過分析可以得出每個反相器在經歷6T時間后又回到初始狀態,所以振蕩周期為6T,同理可得Ⅳ級反相器的周期為2NT。由此推導出Ⅳ級反相器構成的振蕩回路的頻率為1/2NT。

環路反相的次數必須為奇數,否則不滿足巴豪森法則的相位條件。在設計中3或5級反相就能達到比較好的效果,當然如果設計需要可以有更多個反相器級聯。

每個單元的延時時間與流過反相器的電流、反相器的寬長比、電壓、工藝有關。VCO1用單反向器延遲單元串聯的形式組成了最簡單的多諧振蕩器,其最高頻率為3.3 GHz,結構如圖1所示。該振蕩器使用特殊的機理,分為控制和延遲反饋兩部分,利用控制MOS管的短溝效應通過電流鏡決定整個電路的振蕩頻率。由于沒有外加元件,而且結構簡單,極小的寄生參數提高了工作頻率。

2.2 差分環形VCO設計

差分對型VCO主要由差分對延時構成,差分延時單元由壓控電流源、電阻負載以及NMOS管構成。通過控制壓控電流源的電流可以控制環路的振蕩頻率。VCO2采用的這種飽和型雙延時結構的差分延時單元電路,如圖2所示,利用4級該延時單元組成的環形壓控振蕩器電路結構,如圖3所示。在圖2中,電路通過兩個PMOS負載M3和M4組成CMOS鎖存器(Latch),交叉連接的NMOS晶體管M7和M8控制PMOS負載的柵電壓并限制鎖存器的鎖存強度。通過該鎖存器的正反饋,延遲單元工作在全開關狀態,減小了在振蕩周期中開啟時間所占的比例。外加電壓通過交叉連接的NMOS場效應管M7,M8控制PMOS負載場效應管M3,M4的柵極電壓,從而調節該單元的延時;場效應管M5,M6的柵極接附加的級間正反饋,可以減小信號的上升下降時間、提高振蕩器的振蕩頻率并降低相位噪聲。采用4級這種延時單元構成的環形壓控振蕩器結構,如圖3所示,OUT+和OUT-是振蕩器的差分輸出,V_cd是電壓控制端。

評論