基于3GHz CMOS低噪聲放大器優化設計

摘要: 基于0.18 μm CMOS工藝,采用共源共柵源極負反饋結構,設計了一種3 GHz低噪聲放大器電路。從阻抗匹配及噪聲優化的角度分析了電路的性能,提出了相應的優化設計方法。仿真結果表明,該放大器具有良好的性能指標,功率增益為23.4 dB,反向傳輸系數為-25.9 dB,噪聲系數為1.1 dB,1dB壓縮點為13.05 dBm。

1 引 言

現代無線通信技術不斷地朝著低成本、便攜式的方向發展,使得基于CMOS工藝的射頻集成電路成為近年來的研究熱點。在射頻接收機的設計中,要想得到良好的總體系統性能,前端電路的優化設計尤為關鍵。而低噪聲放大器(LNA)作為無線通信系統射頻接收機的第一個功能模塊,其噪聲特性直接影響著整個接收機的靈敏度和信噪比,它必須在一定的功耗條件下,提供足夠的增益、優異的噪聲性能、良好的線性度和輸入輸出匹配。在GHz頻率范圍內,CMOS工藝相比其他工藝有價格低、集成度高、功耗低等優點,利用CMOS工藝來設計射頻集成電路已經得到越來越廣泛的應用,本文即采用CMOS工藝來實現對一種3 GHz低噪聲放大器的優化設計。

在LNA的設計中,應對增益、噪聲系數、輸入阻抗、線性度等幾個關鍵參數采取折衷原則進行處理[1]。T. H. Lee提出了功率約束條件下的設計規范[2],之后又有很多人對CMOS LNA的設計方法進行了研究[3-5]。本文主要從分析LNA的輸入輸出阻抗匹配和噪聲系數的角度出發,針對每個參數的影響因素,分別提出優化的方法,然后綜合考慮其他各項指標,設計出了一種性能良好的低噪聲放大器,并進行了電路仿真和版圖設計。

2 LNA結構

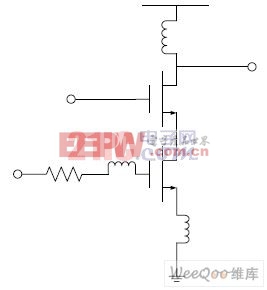

在LNA的設計中,目前廣泛采用的是共源共柵源極負反饋(Cascode)結構,如圖1所示。在此結構中,源極負反饋既能實現輸入阻抗匹配,又能提高系統的穩定性,且具有改善LNA線性度的特點,而M1和M2組成的級聯結構,既提高了電路的輸出阻抗,使電路的增益有較大的提高,又能實現對電路的反向隔離[6],使得輸出端和輸入端互不影響,從而方便了LNA的設計。

圖1 共源共柵源極負反饋結構

評論