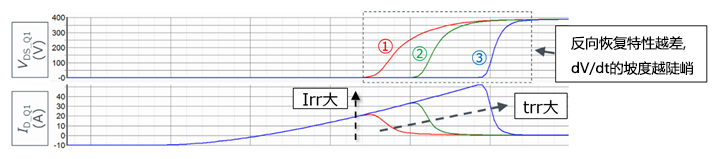

電壓突變的影響--DV/DT以及電流突變的影響--DL/D

信號傳播的整個路徑,包括器件封裝、電路板布局以及連接器等,如果要它們正確地分發轉換時間為TR的數字信號,其頻率響應至少在FKNEE之前都應當是平坦的。如果FKNEE之前某個路徑的頻率響應不是平坦的,在路徑端收到的信號則可能出現上升時間劣化、鼓包、過沖或振鈴。

縮短上升時間將迫使FKNEE的值升高,使得信號傳播的問題更加嚴重。這是過分縮短上升時間的首要缺點。

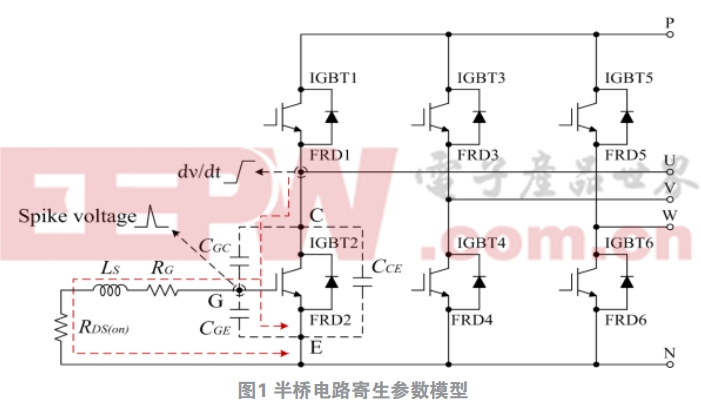

電路的DV/DT還可能影響其他鄰近電路上的信號。這一串擾是由互容機制產生的。兩個鄰近的電路元件總是會有容性的相互作用。參考如下:

“兩個電阻都接地,相應的容性耦合等于0.004,同時感性串擾是0.032。對一個工作在50歐阻抗級別的電路來說,這是一個典型的比率。對于高阻抗電路,涉及的DV/DT較大,DI/DT相對較小,得到的容性耦合相應地比較大。

在門電路的低輸出阻抗的情況下,門電路直接驅動傳輸裝置,感性耦合問題被擴大。在該情形中,總的感性耦合信號能量在遠端終結,而不是如例1.4中一分為二。”

如上所提示,在數字系統中,由互容引起的串擾要遠小于由感引起的串擾。

我們可以把電路最大的DV/DT與它的10~90%上升時間以及電壓幅度△V聯系起來:

評論