基于PXI的高速數字化儀模塊

PXI總線是NI公司在計算機外設總線PCI的基礎上實現的新一代儀器總線,已經成為業界開放式總線的標準,基于PXI總線的數字化儀模塊是現代測試系統中重要的一種數據記錄與處理設備。設計一個雙通道12 bit/250 MHz采樣頻率的高速數字化儀模塊,以高性能FPGA器件為核心,實現對高速A/D的控制以及高速數據處理和存儲,解決了長時間高速記錄信號的測試難題。

1 系統工作原理

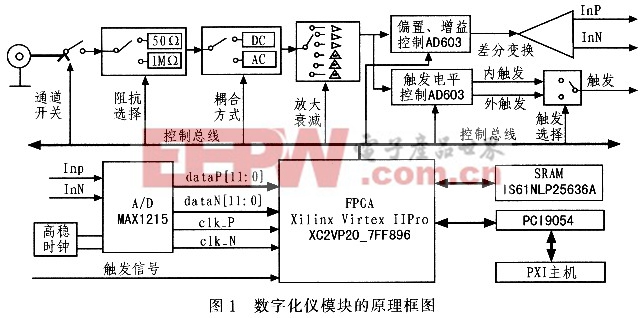

數字化儀模塊主要由前端信號調理通路、模數轉換電路、數據存儲單元、數據采集控制電路、PXI接口電路等部分組成,其原理框圖如圖l所示。

高速模擬信號首先經過信號調理通路進行放大、衰減等處理,將幅度調整到A/D轉換器允許輸入的電壓范圍內,并轉化成LVDS格式的差分信號,然后送到A/D轉換器;FPGA芯片接收A/D輸出的高速數據流,經過降速、抽取濾波等處理后,存儲到數據存儲單元SRAM中,并發出中斷信號,PXI主機響應中斷后經由FPGA將存儲在SRAM中的數據讀入主機內存,完成后續的數據處理和顯示。PXI主機通過PXI總線發送控制命令,經FPGA譯碼后實現對數據采集和調理通路控制。該數字化儀模塊為每個通道預留了4Mb的存儲容量,當組成PXI測試系統時,可以將數據寫入計算機硬盤,實現更長時間的記錄。兩個通道可以獨立工作,也可以相互關聯。采集方式可以有內觸發、外觸發、軟件觸發、通道觸發等多種模式。

2 系統設計實現

2.1 模塊化的FPGA設計

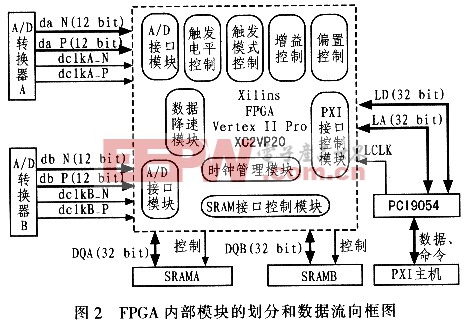

本文所設計的數字化儀是基于高性能FPGA芯片實現的,FPGA承擔了絕大部分的控制和數據處理任務,是本設計的核心器件。對FPGA進行模塊化設計,是大型系統設計的常用方法。合理分割功能模塊,能加快FPGA的開發,也有利于代碼的移植和重復利用。在設計時將FPGA分成高速A/D接口模塊、數據降速模塊、調理通路控制模塊、存儲接口模塊、PXI接口控制模塊等主要功能模塊設計。FPGA內部模塊劃分和數據流向如圖2所示。

A/D接口模塊主要實現FPGA和高速A/D轉換器的互聯,以LVDS格式總線接收數據和采樣時鐘,該部分電路決定數據采集的穩定性,需要從硬件和軟件兩個方面保證;數據降速模塊采用抽取濾波器將信號降低到需要的采樣速率;調理通路控制模塊主要實現對A/D前端電路的控制,包括耦合方式、匹配阻抗選擇、增益自動控制、偏置和觸發電平控制等;PXI接口部分主要實現和PXI主機的通訊譯碼;存儲控制模塊完成對外部SRAM的控制,實現數據緩存;時鐘管理模塊負責采樣時鐘的分頻、倍頻等處理。

2.2 高速數據采集和存儲接口設計

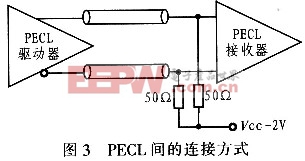

高速數據采集系統的輸入輸出接口設計是尤為重要的,高速IC芯片的相互連接是決定數據采集系統穩定性的關鍵因素之一,低功耗及高的信噪比是有待解決的主要問題。通常實現高速采集系統中芯片間互聯有兩種接口:PECL和LVDS。正電壓射極耦合邏輯PECL(Positive Emit-ter-Coupled Logic)信號的擺幅小,適合于高速數據的串行或并行連接,PECL間的連接一般采用直流耦合,輸出設計為驅動50 Ω負載至(VCC -2V),連接電路如圖3所示。

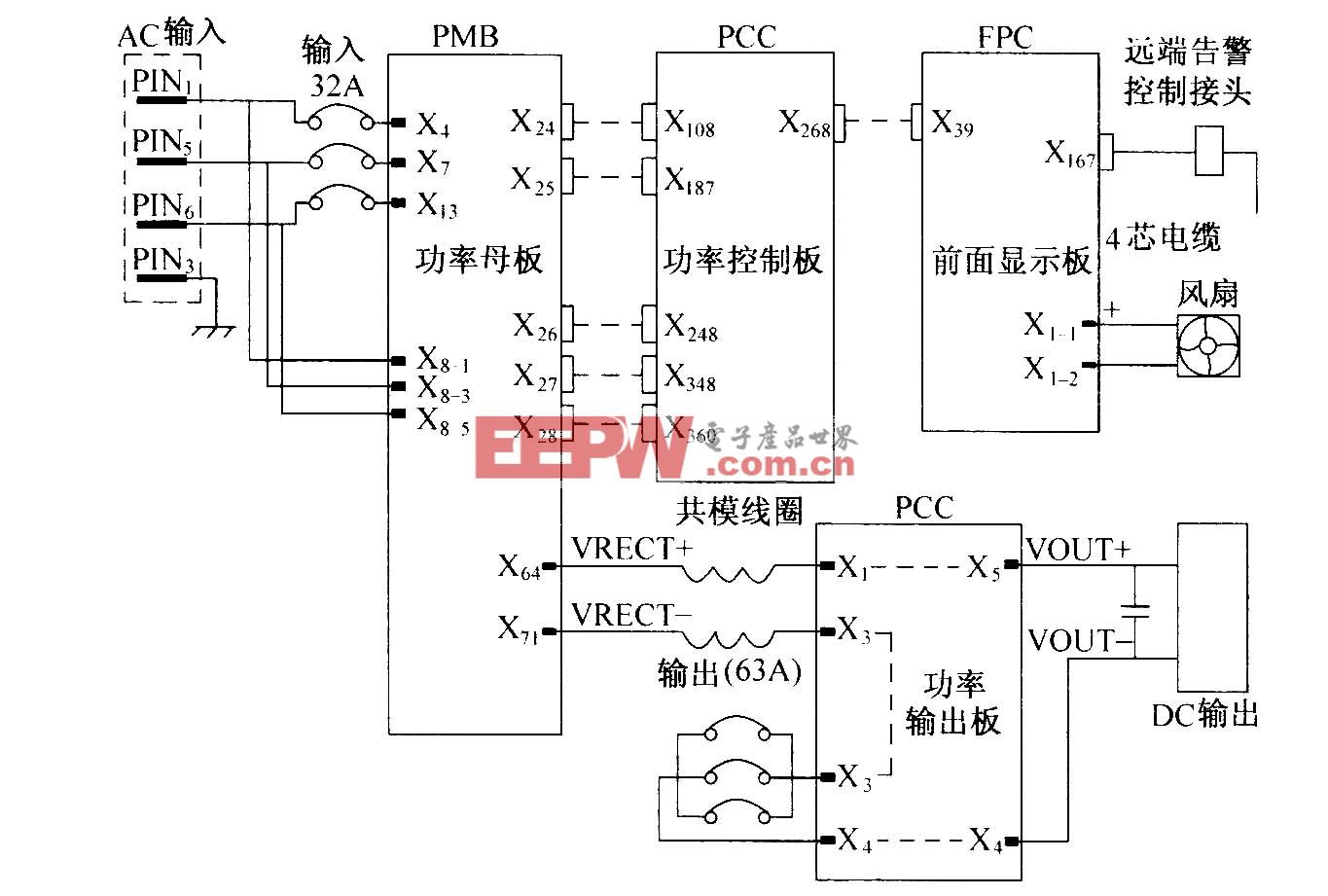

低壓差分信號LVDS(Low Voltage Differential Signal)標準是一種小振幅差分信號技術,它使用非常低的幅度信號(100~450 mV)。通過一對平行的PCB走線或平衡電纜傳輸數據。在兩條平行的差分信號線上流經的電流方向相反,噪聲信號同時耦合到兩條線上,而接收端只關心兩信號的差值,于是噪聲被抵消。由于兩條信號線周圍的電磁場也互相抵消,故差分信號傳輸比單線信號傳輸電磁輻射小很多,從而提高了傳輸效率并降低了功耗。LVDS的輸入與輸出都是內部匹配的,采用直連方式即可,連接方式如圖4所示。

評論