基于AD9957的多波形雷達信號產生器

O 引言

自1971年J.Tierney和C.M.Tader等人首次提出了DDS的概念,作為一種先進的信號產生技術,經過近40年的發展已經廣泛應用于信號源儀器、測量分析儀器、通訊、數字信號處理、工業控制,軟件無線電等領域。目前國內外有關雷達信號產生研究的報道很多,國外的研究做得比較全面:多采用軟硬件相結合的設計方式,系統靈活,并滿足信號實時輸出的要求;設計上采用微處理器和DSP技術提高了系統的性能;采用工業標準的總線結構以及模塊化設計使系統具有良好的通用性、兼容性和可擴充性。

本文討論的基于AD9957的多波形雷達信號產生器實現方案,融合了RS 232串口通信、FPGA和DDS等多種技術,具有數字化、多功能和可編程的特點,并在模塊化設計方面做了一些探索和嘗試性研究。

1 整體方案設計

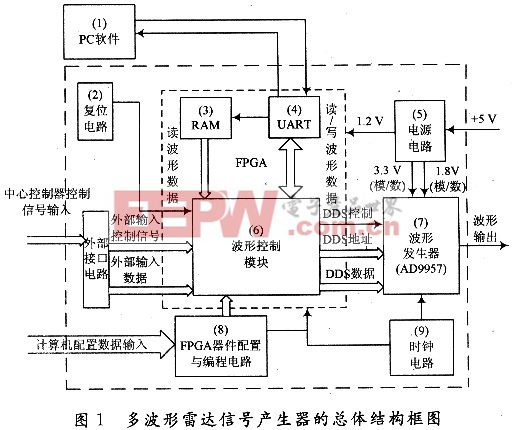

圖1為多波形雷達信號產生器的總體結構框圖。系統主要由PC軟件,波形控制和波形產生三部分構成。圖1中各部分電路簡介如下。

(1)PC軟件編程。應用VC編寫人機交互界面,并用其調用Matlab產生的數據。

(2)復位電路。波形產生器的上電復位或手動復位電路,對波形產生器進行上電初始化或手動初始化。

(3)波形數據庫內存RAM。波形數據庫內存存儲項目要求的所有波形數據,為波形發生器提供需要的波形數據。

(4)UART收發器。完成PC與FPGA之間的通信。

(5)電源電路。為波形產生器、波形控制模塊提供需要的電源。

(6)波形控制模塊。波形控制模塊接收從接口電路輸入的控制信號,按照系統的要求,完成對波形發生器的波形數據配置,輸出需要的波形信號。

(7)波形發生器。波形發生器是信號產生器的波形信號源。

(8)FPGA器件配置與編程電路。FPGA器件配置與編程完成對FPGA器件的數據編程與配置。

(9)時鐘電路。為波形產生器和FPGA提供工作時鐘。

2 主要功能模塊介紹

2.1 數字正交上變頻芯片AD9957介紹

AD9957是美國AD公司(Analog Devices Inc.)生產的具有18位I,Q數據和通路,內置14位數/模轉換器的數字正交上變頻集成電路。AD9 957具有32位相位累加器;內置1 024×32 b RAM,可實現內部調制功能;內部采用1.8 V和3.3 V供電,超低功耗;內置的低噪聲參考時鐘倍頻器允許用低成本、低頻外部時鐘作為系統時鐘,同時仍可提供優良的動態性能。AD9957有3種工作模式:正交調制模式、單頻輸出模式、插值DAC模式。

2.2 UART收發器設計

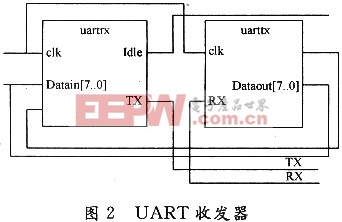

本文中PC與FPGA內部RAM間的通信是通過UART收發器完成的。圖2為通過FPGA設計的UART收發器的頂層原理圖,主要由uartrx(接收模塊)和uarttx(發射模塊)兩部分構成。在完成數據傳輸的同時還可以通過集成到Matlab人機界面中的串口調試程序查看FPGA接收到的數據的正確性,可以簡化程序調試過程。

2.3 波形控制模塊

目前波形控制器通常采用單片機、現場可編程門陣列器件和DSP三種方法來實現。基于系統時序控制要求、電路改動與運行可靠性、開發成本及周期等多個方面綜合考慮,在設計中選擇FPGA來實現波形控制電路。FPGA不僅可以解決電子系統小型化、低功耗、高可靠性等問題,而且其開發周期短、開發軟件投入少、可重復編程使用。圖3為AD9957的波形控制模塊。其中M1和MO是模式控制碼,F[2..O]是工作區選擇碼,S_CLK為串口時鐘,S_DATA為串口數據。圖4為AD9957控制模塊仿真時序圖,從圖中可以看出S_DATA和S_CLK是一一對應的。

評論