高精度3階delta-sigma調制器的設計

2.2 改進的DSM結構圖

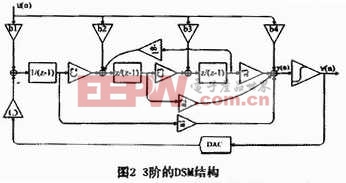

實現傳輸函數的拓撲結構不是唯一的,是多種形式的,一般來說有四種結構使用最為普遍CIFB(cascade-integrator-feedback)、CRFB(cascade-resonator-feedback)、CIFF(cascade-integrator-feedforward)、CRFF(cascade-resonator-feedforward)。如果不需要經過零點優化,可以采用CIFB和CIFF的結構,需要零點經過優化可采用CRFB和CRFF結構。本文是高精度調制器的設計,而經過零點優化的可以得到更好的噪聲整形,實現更高的精度,而CRFF相對CRFB結構在電路設計方面具有結構更為簡單和電路規模更小的優勢,所以采用CRFF結構,如圖2。本文引用地址:http://www.j9360.com/article/187739.htm

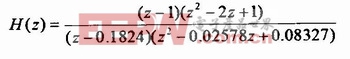

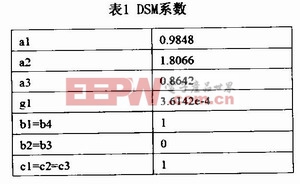

由圖可以看出,輸入信號在比較器前與前饋信號直接相加,實現了STF為1,因此數字濾波器可以不需要考慮基帶補償;al-a3前饋方式實現NTF的極點,降低了積分器輸出的幅度;第三級積分器輸出通過g反饋給第二級積分器,即局部反饋(LFB),這在NTF中引入了共軛零點,挺高了基帶SNR。根據高階穩定的調制器函數的設計方法,設計一個過采樣率為128和3位量化器的3階調制器,圖2中的系數值(a1、a2、a3、a4、bl、b2、b3、b4、cl、c2、c3、g1),由Richard Schreier提供的Matlab Delta-sigma調制器設計工具包可以得出,具體值在表1中給出,表中的數值用于設計NTF和STF的Matlab模型。在實際的數字電路實現時,為了減少芯片面積和設計難度避免使用乘法器,所以這些系數均取2n的近似值,這樣可以用移位相加來代替乘法。利用Richard Schreier提供的Matlab Delta-sigma調制器設計工具包得到帶外增益為6.1,DSM的NTF為

2.3 Verilog語言行為級建模

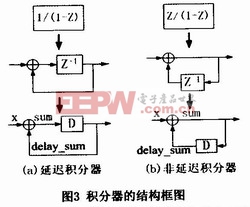

圖2所示的是一種單路差異積分器調制器,可用延遲積分器和非延遲積分器,以及各種前饋和反饋路徑組合而成。在Matlab結構中對應的積分器轉換成Verilog硬件描述框圖的過程如圖3所示

本文使用Verilog硬件語言來實現單回路差異積分調制器,由時鐘控制構成延遲積分器與非延遲積分器的相加動作。assign指令使等式兩邊永遠處于活動狀態,而alwavs指令將會在時鐘正好觸發時將sum的值存入寄存器delay_sum中,因此,所有的積分器將會在每一次時鐘完成時完成一次累加動作。同理,非延遲積分器是由相同的程序代碼組成。實現延遲積分器的程序部分代碼如下表示:

3 模型的仿真結果

圖3給出的是NTF的極點與零點圖。很明顯,NTF的零點均勻地分布在信號基帶中,而不是集中在直流頻率處。圖4給出了輸入幅度范圍與SNR。圖5給出了NTF和STF的幅頻響應。可以看到,帶內信號的衰減幾乎是0,而圖6顯示噪聲的衰減小于-110dB,滿足帶內噪聲的要求。圖7給出了調制器的頻域特性圖。圖8給出的是在輸入為42000,時鐘頻率為8.4MHz的verilog硬件描述語言的仿真結果,可以看出經過2μs后結果趨于穩定。

評論