采樣保持電路中全差分運算放大器的設計與仿真

摘要:本文設計了一種全差分運算放大器,對運算放大器的AC 特性和瞬態特性進行了仿真分析和驗證。該運放采用折疊式共源共柵結構、開關電容共模反饋(SC-CMFB)電路以及低壓寬擺幅偏置電路,以實現在高穩定下的高增益和大輸出擺幅。在Cadence 環境下,基于CSMC 0.6um 工藝模型,進行了仿真分析和驗證。結果表明,運算放大器滿足設計要求。

本文引用地址:http://www.j9360.com/article/187736.htm1 引 言

運算放大器是許多模擬系統和混合信號系統的一個完整部分,伴隨著每一代CMOS 工藝,由于電源電壓和晶體管溝道長度的減小,為運算放大器的設計不斷提出新的挑戰。在采樣保持電路的設計中,運算放大器是最關鍵的模塊之一,其帶寬,擺率,增益,噪聲,失調等性能直接決定了采樣保持電路模塊的速度,精度等性能。

2 折疊共源共柵結構

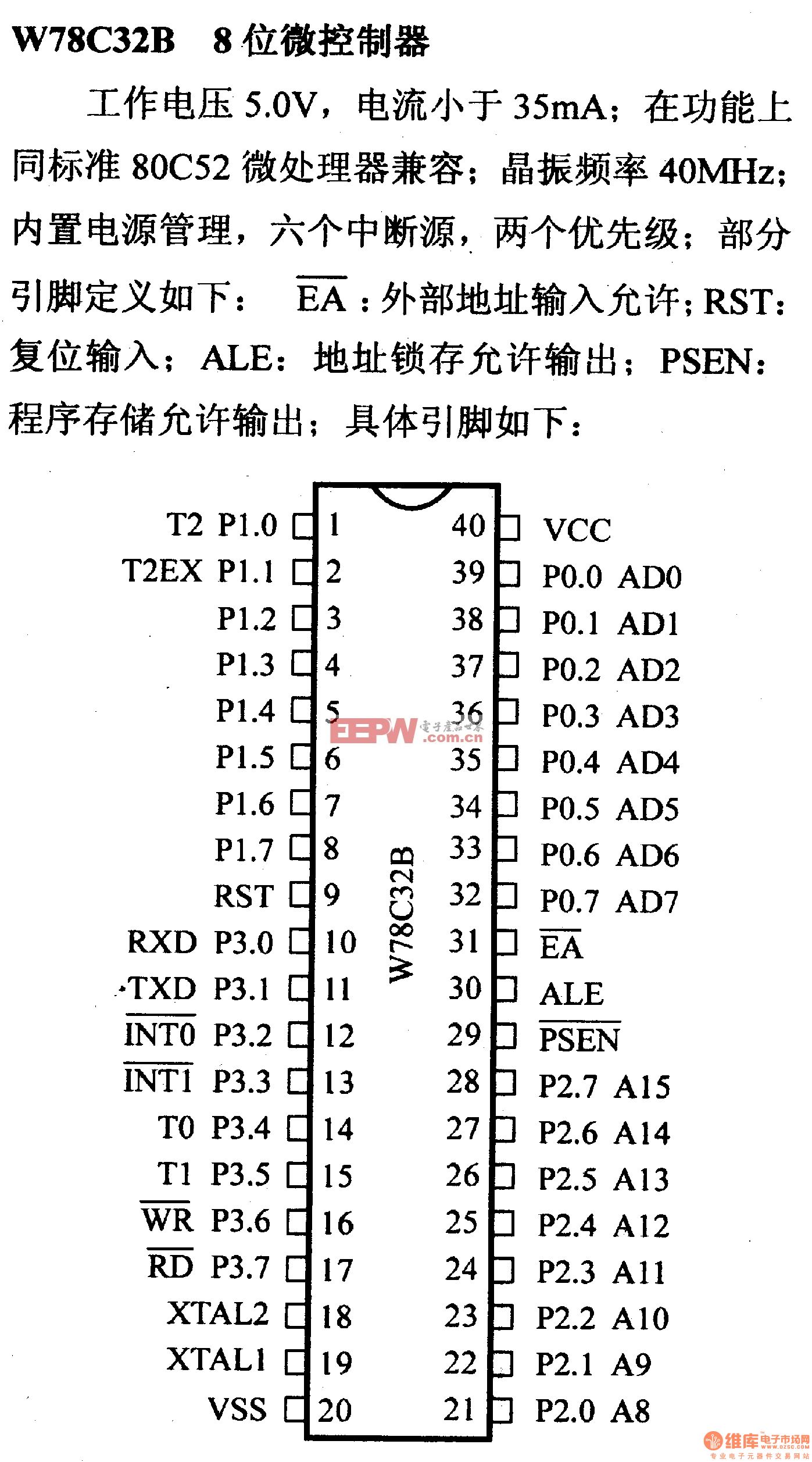

電路結構如圖1 所示。

圖1 折疊共源共柵運算放大器

運算放大器采用折疊共源共柵結構,采用NMOS 輸入差分對MN1 和MN2。MN0 為輸入差分對的尾電流源,向MN1 和MN2 提供直流偏置。MP1 和MP2 為電流源,向輸入管和共源共柵管提供直流偏置。MP3 和MP4 為共源共柵管,用來提高運算放大器的增益。MN3,MN4,MN5 和MN6 是共源共柵電流鏡負載,采用共源共柵結構可以提高輸出阻抗。

負離子發生器相關文章:負離子發生器原理

評論