高壓功率VDMOSFET的設計與研制

摘要:按照功率VDMOSFET正向設計的思路,選取(100)晶向的襯底硅片,采用多晶硅柵自對準工藝,結合MEDICI器件仿真和SUPREM-4工藝仿真軟件,提取參數結果,并最終完成工藝產品試制,達到了500 V/8 A高壓、大電流VDMOSFET的設計與研制要求。結果證明,通過計算機模擬仿真,架起了理論分析與實際產品試制之間的橋渠。相對于原來小批量投片、反復試制的方法,不僅節約了時閽,降低了研制成本,而且模擬結果與實際試制結果之間能夠較好地吻合。針對傳統結終端結構的弊端,提出了一種新型結終端結構,大大提高了產品的擊穿電壓和可靠性。

關鍵詞:功率VDMOSFET;計算機模擬仿真;結終端結構

O 引言

隨著現代工藝水平的提高與新技術的開發完善,功率VDMOSFET設計研制朝著高壓、高頻、大電流方向發展,成為目前新型電力電子器件研究的重點。

本文設計了漏源擊穿電壓為500 V,通態電流為8 A,導通電阻小于O.85 Ω的功率VDMOSFET器件,并通過工藝仿真軟件TSUPREM-4和器件仿真軟件MEDICI進行聯合優化仿真,得到具有一定設計余量的參數值。最后在此基礎上進行生產線工藝流片,逐步調整部分工藝條件,最終實現研制成功。

1 VDMOSFET工作原理

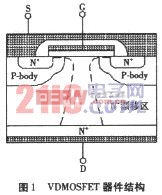

VDMOSFET是電壓控制器件,在柵極施加一定的電壓,使器件溝道表面反型,形成連接源區和漏區的導電溝道。基本工作原理如圖1。

當柵源電壓VGS大于器件的閾值電壓VTH時,在柵極下方的P型區形成強反型層,即電子溝道,此時在漏源電壓VDS的作用下,N+源區的電子通過反型層溝道,經由外延層(N-漂移區)運動至襯底漏極,從而形成漏源電流。

當VGS小于閾值電壓VTH時,柵極下方不能形成反型層溝道。由于外延層(N-漂移區)的濃度較低,則耗盡層主要在外延層(N-漂移區)一側擴展,因而可以維持較高的擊穿電壓。

2 參數設計

2.1 外延層電阻率和厚度

外延層的電阻率ρ越大(摻雜濃度Nepi越小),則器件的擊穿電壓越大。然而,導通電阻Ron也相應增大。因此,在滿足擊穿要求的前提下,ρ越小(Nepi越大)越好;而從導通電阻的角度考慮,又限定了該電阻率的最大值。所以將在計算機仿真過程中,調整P-body的注入劑量、推阱時間和外延層電阻率、厚度,得出最佳的結構參數。

評論