高速高精度鐘控比較器的設計

在現代通信和信號處理系統中,高性能A/D轉換器作為連接模擬和數字世界的重要通道被廣泛應用于醫學圖像、高速數據變換及QAM調制器等重要設計領域。比較器是模數轉換器設計的核心單元,其精度、速度、失調電壓和回饋噪聲等因素直接影響著系統模塊的整體性能。傳統的預放大鎖存比較器通過采用3級或3級以上級聯的預放大器結構降低比較器的傳輸延時和回饋噪聲,但這些指標是以較高的功耗和增加芯片面積為代價的。典型的A-B型動態鎖存比較器具有高速、低功耗的特點,但該結構存在著較大的回饋噪聲和失調電壓,限制了比較器精度的提高。綜合考慮以上因素,基于TSMC 0.18μm CMOS標準工藝,本文設計了一種可應用于高速高精度A/D轉換器的比較器結構,給出了提高比較速度和降低回饋噪聲的理論和方法,并基于此進行了電路的設計與優化。

1 比較器電路設計

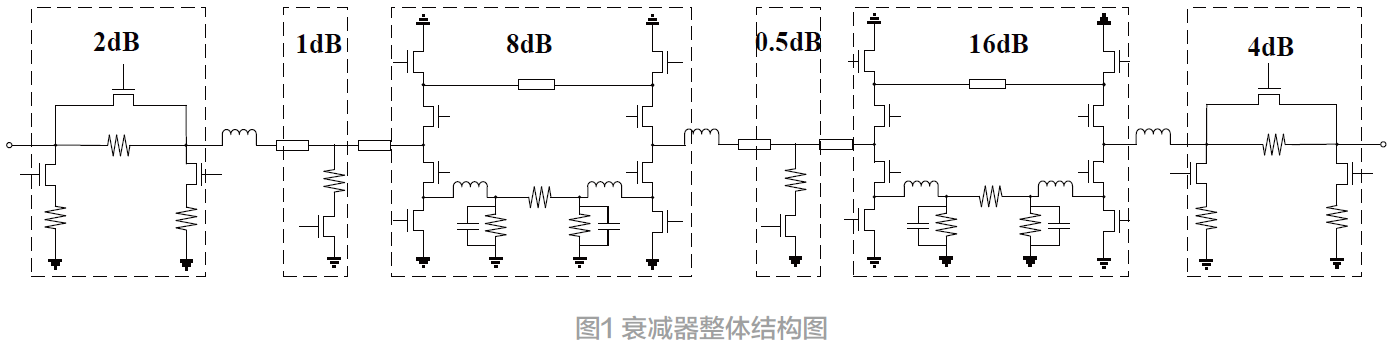

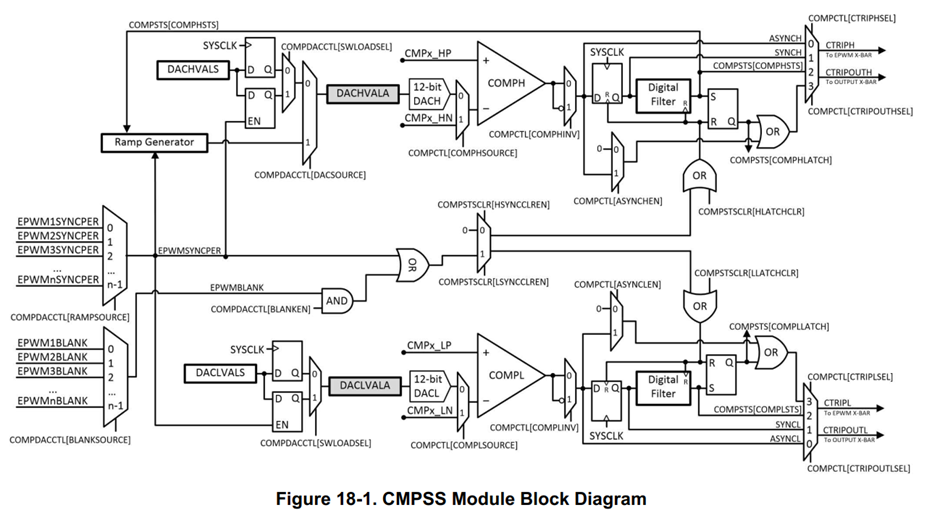

本文設計的高速高精度鐘控比較器從功能上可劃分為3級,包括預放大級,鐘控比較級,輸出緩沖級,如圖1所示。輸入信號通過預放大級電路放大,并由時鐘信號控制把放大后的信號傳輸到鐘控比較級進行再生比較,最后利用正反饋結構的輸出緩沖級電路將輸出電壓迅速轉化成邏輯電平。

1.1 預放大級

為了滿足高速、高精度的要求,預放大器的設計原則是高帶寬低增益。單純的以MOS二極管和電流源為負載的放大器具有有限的增益帶寬積,不能同時兼顧速度和精度的要求,使用二極管和電流源負載的混合結構可以滿足良好的增益和帶寬的折衷。

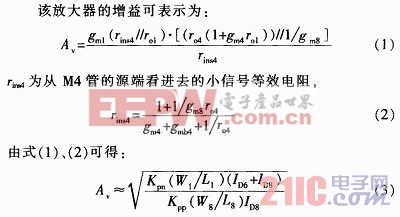

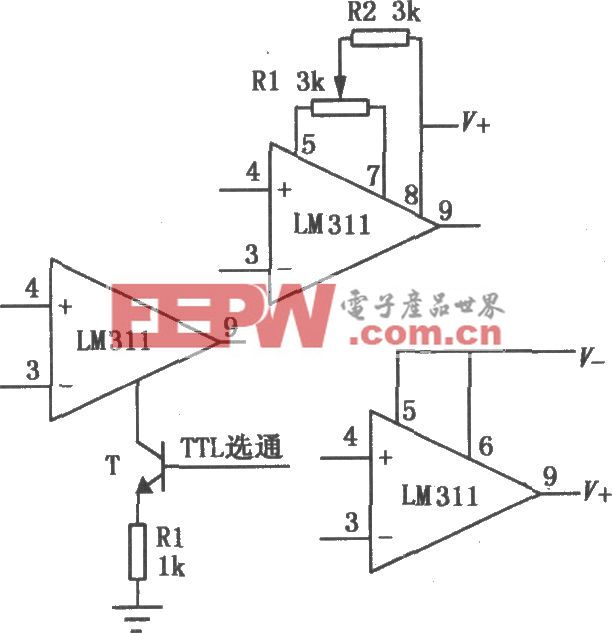

針對圖l中預放大級,VM1、VM2構成差分放大管,二極管方式連接的MOS管VM8,VM9為差分對的有源負載,增加PMOS鏡像電流源VM6、VM7的目的是使輸入晶體管偏置電流的一部分由PMOS電流源提供,這樣可以通過減小電流而不是減小寬長比來降低負載管的跨導,進而提高差動增益。VM4、VM5為鐘控開關晶體管,當時鐘信號clk為高電平時,其與輸入差分對構成共源共柵結構,提高電路對輸入信號的放大能力;當時鐘信號clk為低電平時,其可以有效隔離輸入信號與再生節點饋通的回饋噪聲,這對保證電路的性能非常重要,預放大電路的小信號模型如圖2所示。

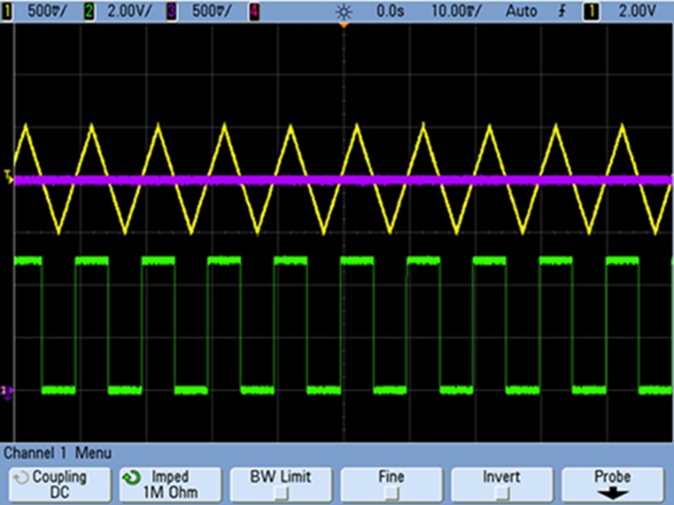

從式(3)可以看出,通過合理調節管子的寬長比和電流源注入的電流值可調節放大器的增益和頻率特性。需要注意的是,為同時滿足高速比較器對響應時間的要求,設計中在保證增益的同時盡量增加預放大器的帶寬。該預放大器的增益、帶寬仿真結果如圖3所示,增益為18.352 dB,-3 dB帶寬為1.122 GHz。

評論