加減法運算電路的設計方法

解出R’=40kΩ。

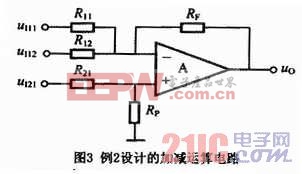

例2,試設計實現u=2u121-3u111-u112運算關系的加減運算電路。

將所要實現的運算關系式與式(4)對比,確定式(4)中各輸入信號的比例系數為本文引用地址:http://www.j9360.com/article/187655.htm

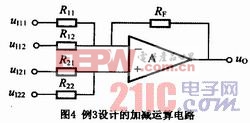

例3,試設計實現u0=2u121+u122-1.5u111-0.5u112運算關系的加減運算電路。

將所要實現的運算關系式與式(4)對比,確定式(4)中各輸入信號的比例系數為

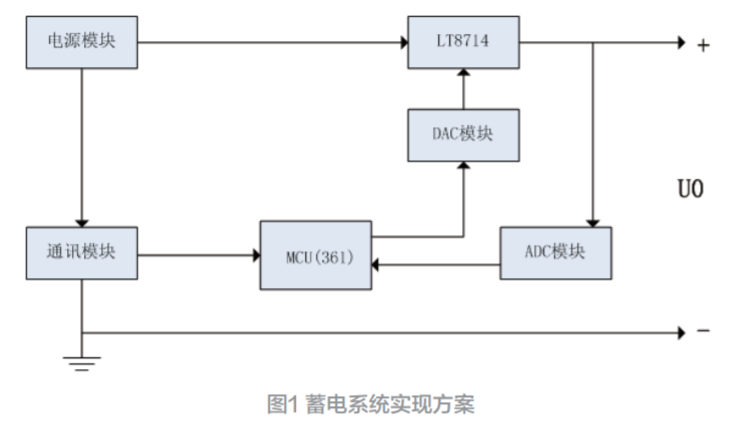

確定所設計電路的形式為圖1中去掉電阻R’及Rp,按四個輸入信號重畫如圖4所示。

選取RF=150kΩ,代入各輸入信號的比例系數表達式中,解出

4 結語

本文討論了加減運算電路的構成形式及比例系數適應范圍,從而可實現輸入信號以任意比例系數參與運算的電路設計,使運算電路具有普遍適用性。

DIY機械鍵盤相關社區:機械鍵盤DIY

電流傳感器相關文章:電流傳感器原理

評論