PCM串行數據流同步時鐘提取設計

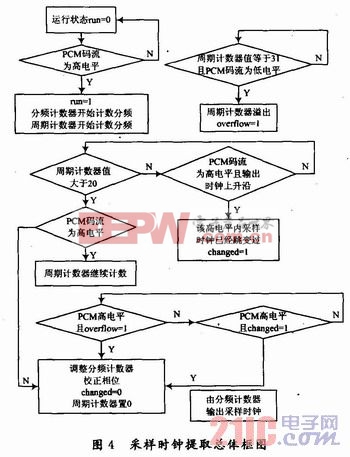

模塊使用同步時序設計方式實現,所有工作在輸入全局時鐘信號clk上升沿的驅動下進行,包括復位功能同樣為同步工作。在clk驅動下,復位信號低電位時系統復位,各寄存器進行初始化工作置初值,復位信號結束后,run標志位置1模塊開始工作。系統模塊框圖如圖4所示。本文引用地址:http://www.j9360.com/article/187615.htm

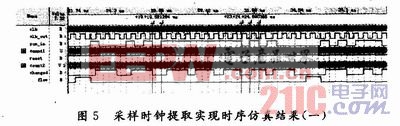

以Altera的EPM7128SLC84型CPLD作為目標器件,在集成開發環境QuartusⅡ中對上述VerilogHDL語言描述的時鐘信息提取模塊編譯綜合布局布線后進行時序仿真,得到仿真波形如圖5所示。

為了方便對異常處理功能進行驗證,仿真時使用輸入時鐘約為PCM碼流速率的7.5倍,由圖5中可以看出,設計對于輸出采樣時鐘校正有很明顯效果。

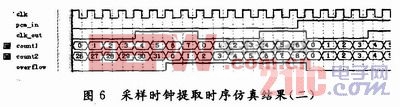

圖6中則是使用完全8倍時鐘輸入的仿真結果,結果完全符合設計目標。

3 結論

本文中給出的串行數據流采樣時鐘提取方法及其實現,不僅局限于文中所特定語音通信PCM30/32路系統,對類似的已知速率串行數據流異步接收系統均適用。該方法能夠有效地提取出數據流中包含的發送端時鐘信息,并消除接收端本地時鐘與之相位偏差、時鐘頻率偏差等因素導致的工作穩定性不高以至接收數據錯誤等不良結果,具有較好的適應性。

評論