一種基于PCI總線的反射內存卡設計

1 引言

本文引用地址:http://www.j9360.com/article/187535.htm對實時傳輸, 傳統的以太網絡由于傳輸協議開銷的不確定性, 很難滿足實時網絡的要求, 實時網絡是一種應用于高實時性要求的專用網絡通信技術, 一般采用基于高速網絡的共享存儲器技術實現。除了具有嚴格傳輸確定性和可預測性外, 還具有傳輸速度高、通訊協議簡單、軟硬件平臺適應性強、可靠的傳輸糾錯能力、支持中斷信號的傳輸等特點。鑒于以上原因, 設計一款反射內存卡, 寫入一個節點的內存的數據可以通過網絡硬件傳輸到其它所有的節點。

2 硬件設計

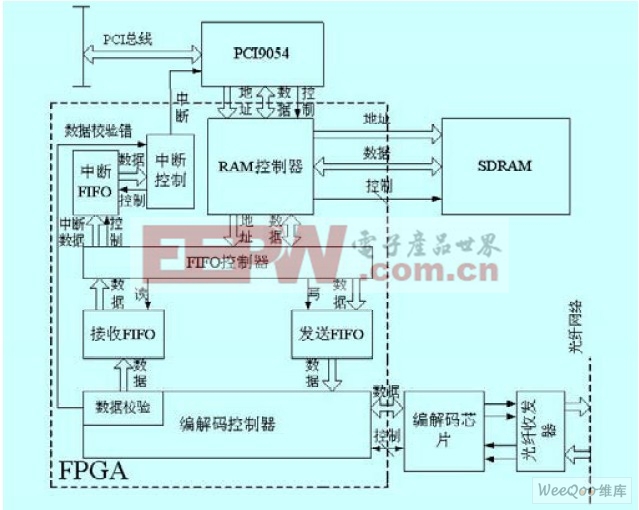

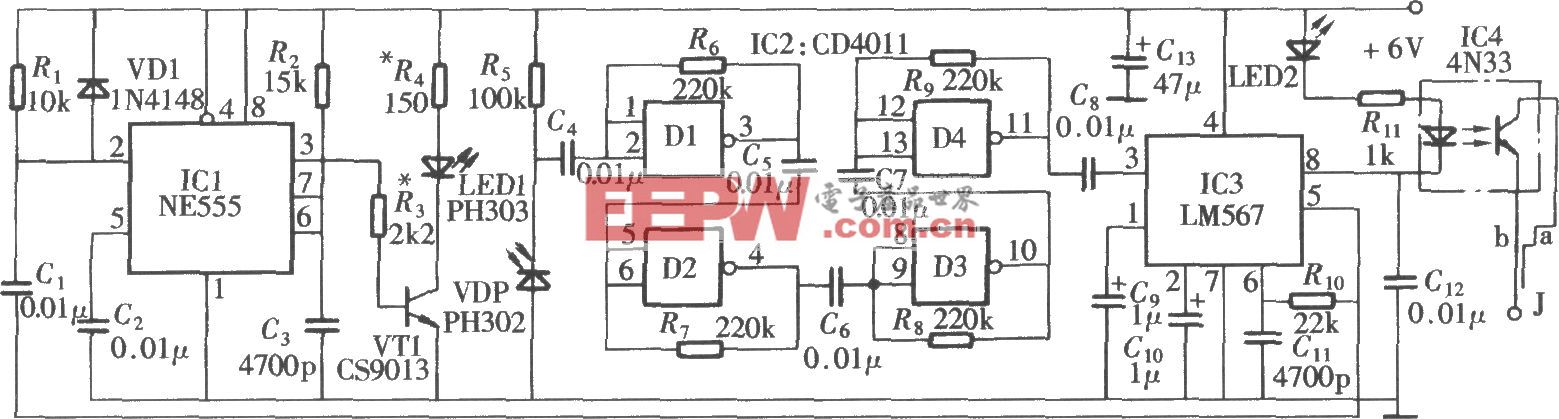

反射內存卡系統的總體框圖如圖1 所示, 主要由5部分組成:FPGA、PCI 接口、SDRAM、數據編解碼電路、光纖收發電路。

其中,FPGA 內部包含SDRAM控制器和FIFO 控制器、編解碼控制器、接收FIFO、發送FIFO、中斷FIFO及中斷控制等。FPGA 選用Cyclone II 系列的EP2C35F484C7;PCI 選用PLX 公司的PCI9054,能夠提供兩個獨立的DMA 引擎,每個都可以進行讀寫,在一個DMA 讀取數據的同時另一個DMA 可以寫入數據,加快系統工作速度; 編解碼芯片選用安捷倫的H D M P -1636A,提供十位的并行IO,串行數據傳輸速率達1062.5MBd,負責數據串并行和并串行轉換,以便與光纖收發器內部數據格式進行匹配; 光纖收發器選用安捷倫的HFBR-57L5AP,支持多模光纖,串行傳輸速率達1.0625Gb/s,負責將電信號轉化為光信號, 通過光纖向下一節點傳輸。

2.1 SDRAM 控制器

與雙端口RAM 相比,SDRAM 容量大、價格低,采用128M 的SDRAM 作為反射內存卡的數據存儲器。由于SDRAM 讀寫不能同時進行,且需要刷新維護,因此,需要設計SDRAM 控制器。

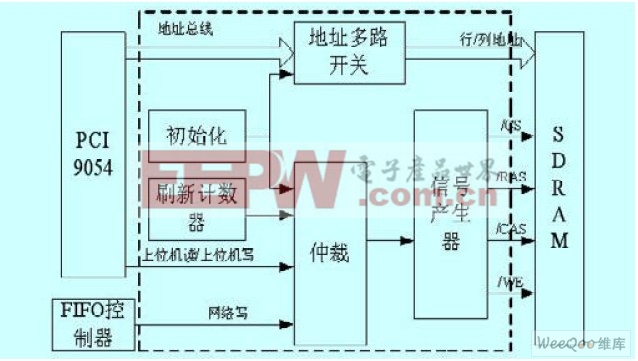

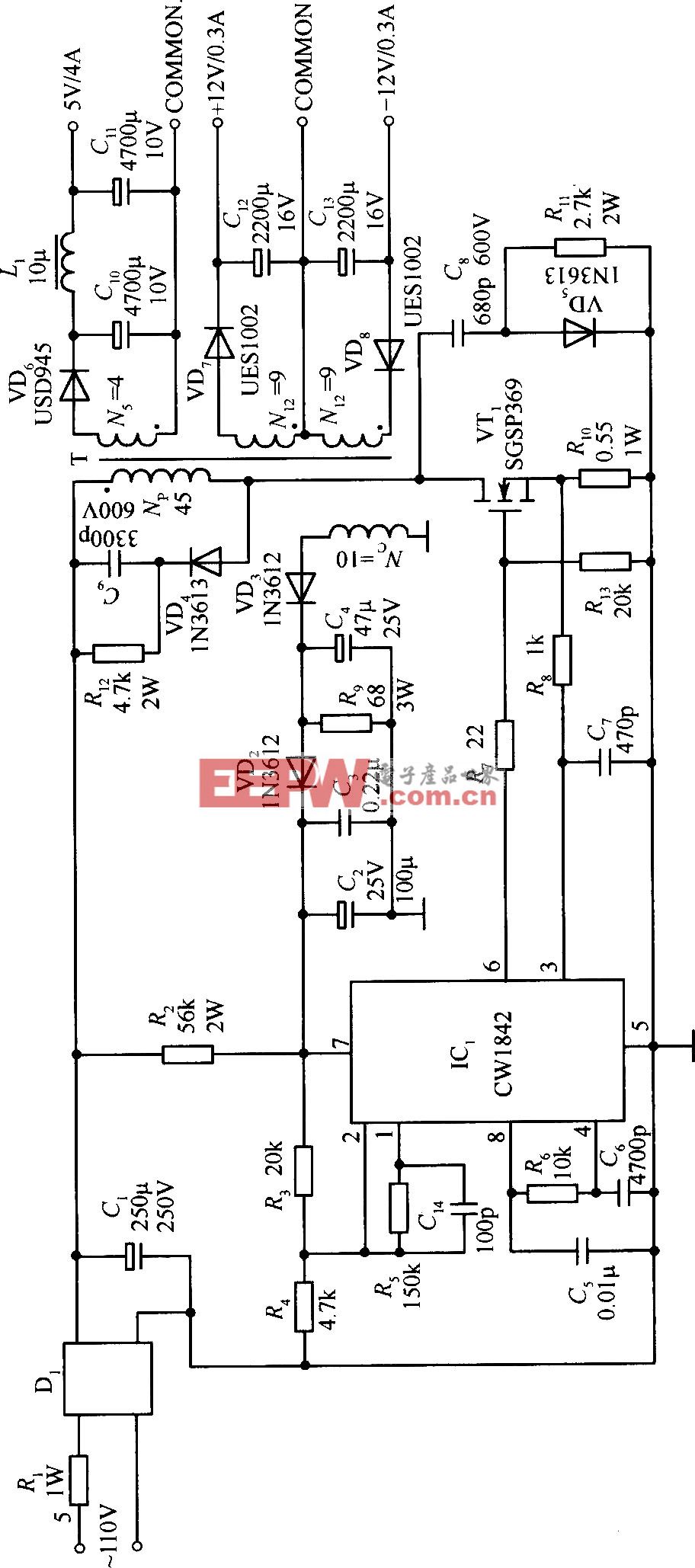

SDRAM 控制器實現對SDRAM 的讀寫控制與仲裁,提供類似于雙端口RAM 的外部接口。SDRAM 控制器內部由初始化模塊、刷新計數器、地址多路開關、仲裁及信號產生器等組成,SDRAM 控制器結構如圖2 所示。

圖2 SDRAM 控制器結構圖

SDRAM 控制器內部各模塊功能如下:

(1) 初始化模塊在上電之后對SDRAM 的模式寄存器進行設置;(2) 刷新計數器對SDRAM 進行定時刷新;(3) 地址多路開關將地址總線上的地址轉化為SDRAM 的行列地址;(4) 仲裁機構要對上位機讀、上位機寫、網絡寫和刷新等操作做出仲裁。當讀寫和刷新同時產生時, 先完成相應的讀寫操作然后再刷新, 而上位機讀、上位機寫、網絡寫這三種操作的優先級從高到低依次是網絡寫、上位機讀、上位機寫;(5) 信號產生器根據不同的讀寫操作產生不同的讀寫信號, 從而SDRAM 可以正常工作, 而不發生讀寫沖突。

2.2 FIFO 控制器

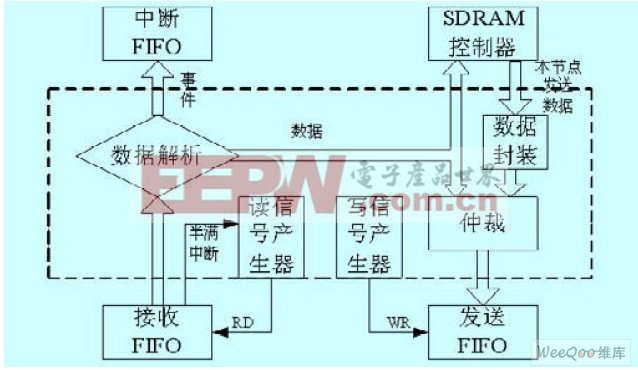

在峰值速率下進行數據傳輸,SDRAM 存儲器很難達到要求,所以使數據經過FIFO 緩存后發送或接收,可以降低了對存儲器傳輸速率的要求, 實現較高的傳輸速率。設計了FIFO 控制器,它由數據解析、數據封裝、仲裁、讀信號產生器、寫信號產生器組成。FIFO 控制器結構如圖3 所示。

圖3 FIFO 控制器結構圖

評論