SPI總線的特點、工作方式及常見錯誤解答

圖6模式錯誤的檢測

4.3 溢出錯誤(OVR)

溢出錯誤表示連續傳輸多個數據時,后一個數據覆蓋了前一個數據而產生的錯誤。

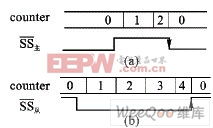

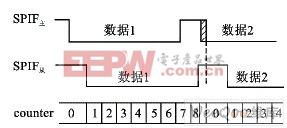

狀態標志SPIF表示的是數據傳輸正在進行中,它對數據的傳輸有較大的影響。主器件的SPIF有效由數據寄存器的空標志SPTE=0產生,而從器件的SPIF有效則只能由收到的第一個SCK的跳變產生,且又由于從器件的SPIF和主器件發出的SCK是異步的,因此從器件的傳輸標志SPIF從相對于主器件的傳輸標志SPIF主有一定的滯后。如圖7所示,在主器件連續發送兩個數據的時候將有可能導致從器件的傳輸標志和主器件下一個數據的傳輸標志相重疊(圖7中虛線和陰影部分),第一個收到的數據必然被覆蓋,第二個數據的收/發也必然出錯,產生溢出錯誤。

圖7溢出錯誤

通過對從器件的波形分析發現,counter=8后的第一個時鐘周期,數據最后一位的傳輸已經完成。在數據已經收/發完畢的情況下,counter=8狀態的長短對數據的正確性沒有影響,因此可以縮短counter=8的狀態,以避免前一個SPIF和后一個SPIF相重疊。這樣,從硬件上避免了這一階段的溢出錯誤。

但是,如果從器件工作速度不夠快或者軟件正在處理其他事情,在SPI接口接收到的數據尚未被讀取的情況下,又接收到一個新的數據,溢出錯誤還是會發生的。此時,SPI接口保護前一個數據不被覆蓋,舍棄新收到的數據,置溢出標志OVR=1;另外發出中斷信號(如果該中斷允許),通知從器件及時讀取數據。

4.4 偏移錯誤(OFST)

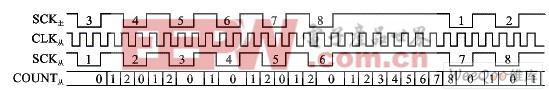

SPI接口一般要求從器件先工作,然后主器件才開始發送數據。有時在主器件往外發送數據的過程中,從器件才開始工作,或者SCK受到外界干擾,從器件未能準確地接收到8個SCK。如圖8所示,從器件接收到的8個SCK其實是屬于主器件發送相鄰的兩個數據的SCK主。這時,主器件的SPIF和從器件的SPIF會發生重疊,數據發生了錯位,從器件如果不對此進行糾正的話,數據的接收/發送便一直地錯下去。

圖8偏移錯誤

在一個數據的傳輸過程中,SPR是不允許改變的,即SCK是均勻的,而從圖5可以看出,從器件接收到的8個SCK并不均勻,它們是分別屬于兩個數據的,因此可以計算SCK的占空時間來判斷是否發生了偏移錯誤。經分析,正常時候SCK=1時的時鐘周期數n的取值滿足如下關系:

但由于主從時鐘之間是異步的,并且經過了取整,所以正常時候SCK=1時的時鐘周期計數值COUNT應滿足:

比如在圖5中,COUNT的最大值COUNT(max)=2或者1,都可認為是正常的。但當出現COUNT(max)=8時,可以判定出現了偏移錯誤。在實際設計中,先記錄下第一個COUNT(max)的值,如果后面又出現與記錄值相差1以上的COUNT(max)出現,可知有偏移錯誤OFST發生。SPI接口在“不均勻”的地方令SPIF=1,然后準備等待下一個數據的第一個SCK。其中COUNT的位數固定為8位,為了避免溢出時重新從00H開始計數,當計數達到ffH時停止計數。

4.5 其他錯誤

設定不當,或者受到外界干擾,數據傳輸難免會發生錯誤,或者有時軟件對錯誤的種類判斷不清,必須要有一種方法強制SPI接口從錯誤狀態中恢復過來。在SPI不工作,即SPEN=0的時候,清除SPI模塊內部幾乎所有的狀態(專用寄存器除外)。如果軟件在接收數據的時候,能夠發現數據有錯誤,無論是什么錯誤,都可以強制停止SPI的工作,重新進行數據傳輸。例如,在偏移錯誤(OFST)中,如果SPR2、SPR1和SPR0的設置適當,也可以使SCK顯得比較“均勻”。SPI接口硬件本身不可能檢測到有錯誤,若用戶軟件能夠發現錯誤,這時就可以強制停止SPI的傳輸工作,這樣就可以避免錯誤一直持續下去。

在應用中,如果對數據的正確性要求較高,除了要在軟件上滿足SPI接口的時序要求外,還需要在軟件上作適當的處理。

5.設計SPI總線控制器

目前的項目中使用了SPI總線接口的FLASH存儲器存儲圖像數據。FLASH的SPI總線頻率高達66M,但MCU的頻率較低,晶振頻率7.3728M,SPI最大頻率為主頻1/2。對于320*240*16的圖像讀取時間為333ms,而且還忽略了等待SPI傳輸完成、寫顯存、地址坐標設定等時間。實際測試約為1s。成為GUI設計的極大瓶頸。由于TFT驅動是自己FPGA設計的,資源尚有余量,決定把SPI控制器(主)及寫圖像部分邏輯放入FPGA中用硬件完成。

首先接觸到的是SPI的SCK時鐘頻率問題。FPGA的頻率是48M,未使用PLL。能否以此頻率作為SCK頻率呢?要知道所有的MCU提供的SPI頻率最大為主頻的1/2!為什么呢?查過一些資料后發現,SPI從機接收數據并不是以SCK為時鐘的,而是以主頻為時鐘對SCK和MISO進行采樣,由采樣原理得知SCK不能大于1/2主頻,也就有了MCU提供最大master頻率是1/2主頻,最大slaver頻率是1/4主頻。FPGA在只作為主機時能否實現同主頻一樣頻率的SCK呢??答案貌似是肯定的!但我還是有點擔心,用組合邏輯控制SCK會不會出現較大毛刺影響系統穩定性呢?

晶振相關文章:晶振原理

評論