SPI總線的特點、工作方式及常見錯誤解答

時序詳解:

CPOL:時鐘極性選擇,為0時SPI總線空閑為低電平,為1時SPI總線空閑為高電平

CPHA:時鐘相位選擇,為0時在SCK第一個跳變沿采樣,為1時在SCK第二個跳變沿采樣

工作方式1:

當CPHA=0、CPOL=0時SPI總線工作在方式1。MISO引腳上的數據在第一個SPSCK沿跳變之前已經上線了,而為了保證正確傳輸,MOSI引腳的MSB位必須與SPSCK的第一個邊沿同步,在SPI傳輸過程中,首先將數據上線,然后在同步時鐘信號的上升沿時,SPI的接收方捕捉位信號,在時鐘信號的一個周期結束時(下降沿),下一位數據信號上線,再重復上述過程,直到一個字節的8位信號傳輸結束。

工作方式2:

當CPHA=0、CPOL=1時SPI總線工作在方式2。與前者唯一不同之處只是在同步時鐘信號的下降沿時捕捉位信號,上升沿時下一位數據上線。

工作方式3:

當CPHA=1、CPOL=0時SPI總線工作在方式3。MISO引腳和MOSI引腳上的數據的MSB位必須與SPSCK的第一個邊沿同步,在SPI傳輸過程中,在同步時鐘信號周期開始時(上升沿)數據上線,然后在同步時鐘信號的下降沿時,SPI的接收方捕捉位信號,在時鐘信號的一個周期結束時(上升沿),下一位數據信號上線,再重復上述過程,直到一個字節的8位信號傳輸結束。

工作方式4:

當CPHA=1、CPOL=1時SPI總線工作在方式4。與前者唯一不同之處只是在同步時鐘信號的上升沿時捕捉位信號,下降沿時下一位數據上線。

4.SPI總線常見錯誤

4.1 SPR設定錯誤

在從器件時鐘頻率小于主器件時鐘頻率時,如果SCK的速率設得太快,將導致接收到的數據不正確(SPI接口本身難以判斷收到的數據是否正確,要在軟件中處理)。

整個系統的速度受三個因素影響:主器件時鐘CLK主、從器件時鐘CLK從和同步串行時鐘SCK,其中SCK是對CLK主的分頻,CLK從和CLK主是異步的。要使SCK無差錯無遺漏地被從器件所檢測到,從器件的時鐘CLK從必須要足夠快。下面以SCK設置為CLK主的4分頻的波形為例,分析同步串行時鐘、主時鐘和從時鐘之間的關系。

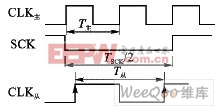

圖4主從時鐘和SCK的關系

如圖4所示,當T

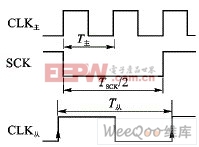

圖5主從時鐘和SCK的關系

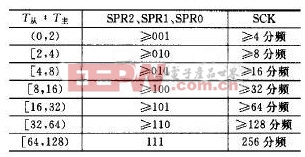

根據以上的分析,SPR和主從時鐘比的關系如表1所列。

表1 SPR的設置和主從時鐘周期比值之間的關系

在發送數據之前按照表1對SPR進行設置,SPR設定錯誤可以完全避免。

4.2 模式錯誤(MODF)

模式錯誤表示的是主從模式選擇的設置和引腳SS的連接不一致。

器件工作在主模式的時候(MSTR=1),它的片選信號SS引腳必須接高電平。在發送數據的過程中,如果它的SS從高電平跳至低電平,在SS的下降沿,SPI模塊將檢測到模式錯誤,對MODF位置1,強制器件從主模式轉入從模式(即令MSTR=0),清空內部計數器counter,并結束正在進行的數據傳輸,如圖6(a)所示。

對從模式(MSTR=0),在沒有數據傳送的時候,SS高電平表示從器件未被選中,從器件不工作,MISO輸出高阻;在數據傳輸過程中,片選信號SS必須接低電平,且SS不允許跳變。如果SS從低電平跳到高電平,在SS的上跳沿,SPI模塊也將檢測到模式錯誤,清空內部計數器counter,并結束正在進行的數據傳輸。直到SS恢復為低電平,重新使SPEN=1時,才重新開始工作,如圖6(b)所示。

晶振相關文章:晶振原理

評論