高di/dt負載瞬態的電源及其分配系統設計

就許多中央處理器(CPU)而言,規范要求電源必須能夠提供大而快速的充電輸出電流,特別是當處理器變換工作模式的時候。例如,在1V的系統中,100A/uS負載瞬態可能會要求將電源電壓穩定在3%以內。解決這一問題的關鍵就是要認識到這不僅僅是電源的問題,電源分配系統也是一個重要因素,而且在一款解決方案中我們是很難將這二者嚴格地劃清界限。

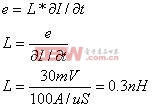

本文引用地址:http://www.j9360.com/article/186521.htm這些高di/dt要求的意義就在于電壓源必須具有非常低的電感。重新整理下面的公式并求解得到允許的電源電感:

在快速負載電流瞬態通道中電感僅為0.3nH。為了便于比較,我們來看一個四層電路板上的0.1英寸(0.25cm)寬電路板線跡所具有的電感大約為0.7nH/英寸(0.3nH/cm)。IC封裝中接合線的典型電感在1nH范圍內,印刷電路板的過孔電感在0.2nH范圍內。

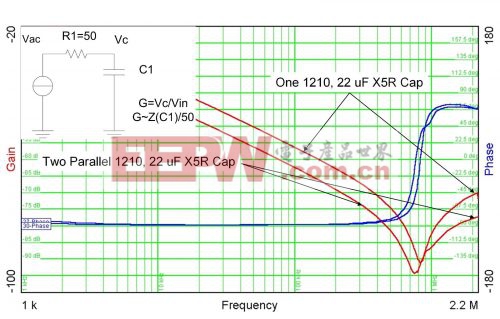

此外,還有一個與旁路電容有關的串聯電感,如圖1所示。頂部的曲線是貼裝在四層電路板上的一個22uF、X5R、16V、1210陶瓷電容的阻抗。正如我們所期望的那樣(100kHz以下),阻抗隨著頻率的增加而下降。然而,在800kHz時有一個串聯電感,此時電容會變得有電感性。該電感(其可以從電容值和諧振頻率計算得出)為1.7nH,其大大高于我們0.3nH的目標值。幸運的是,您可以使用并聯電容以降低有效的ESL。圖1底部的曲線為兩個并聯電容的阻抗。有趣的是諧振變得稍微低了一些,這表明有效電感并不是絕對的一半。基于諧振頻率,就兩個并聯的電容而言,新電感則為1.0nH或ESL下降40%,而非下降50%。這一結果可以歸結為兩個原因:互連電感和兩個電容之間的互感。

圖1并聯電容阻抗寄生現象衰減效果

電流通道的環路尺寸在一定程度上決定了連接組件中的寄生電感,組件尺寸決定了環路的面積。尺寸與電感相關系數如表1所示,其顯示了各種尺寸陶瓷表面貼裝電容的電容電感。一般來說,體積越大的電容具有更大的電感。該表不包括電路板上貼裝電容的電感,在我們以前的測量中該電感由1nH增加到了1.7nH。另一個有趣的問題是端接的位置對電感有很大的影響。0805電容在電容的較短一側有端接而0508電容則在較長的一側有端接。這幾乎將電流通道分為了兩半,從而大降低了電感。這種變化了的結構將電感降低了四分之一。

表1陶瓷SMT電容尺寸會影響寄生電感

尺寸

ESL(nH)

0603

0.6

0805

0.8

0508

0.2

1206

1.0

0612

0.2

1210

1.0

總之,高di/dt負載需要仔細考慮旁路問題以保持電源動態穩壓。表面貼裝電容需要非常靠近負載以最小化其互連電感。電容具有可能避免大量去耦的寄生電感。降低這一寄生電感的并聯電容是有效的,但互連和互感減弱了這一效果。使用具有更短電流通道的電容也是有效的。這可以用體積較小的部件或具有交流端接(其使用了更短的尺寸用于電流)的部件來實施。

更多資訊請關注:21ic模擬頻道

評論