多維設計技術力促3D芯片

您可能聽說過這樣的宣傳:隨著目前還是平面結構的裸片向多層結構的過渡,半導體制造基礎在今后幾年內將發生重大轉變。為了使這種多層結構具有可制造性,全球主要半導體組織作出了近10年的不懈努力,從明年開始三維(3D)IC將正式開始商用化生產——比原計劃落后了好幾年。

本文引用地址:http://www.j9360.com/article/186492.htm芯片制造商用了好幾年時間才使得用于互連3DIC的硅通孔(TSV)技術逐漸成熟。雖然硅通孔技術一直用于2D任務,比如將數據從平面芯片的前面傳送到反面的凸塊,但使用堆疊裸片的3DIC已經排上議事日程。

去年舉行的國際固態電路會議主要討論的內容是“近似3D”芯片,如三星公開宣揚的1Gbit移動DRAM(計劃到2013年躍升至4Gbit)。三星的這種2.5D技術非常適合位于系統級芯片之上且帶硅通孔和微凸塊的堆疊式DRAM裸片。

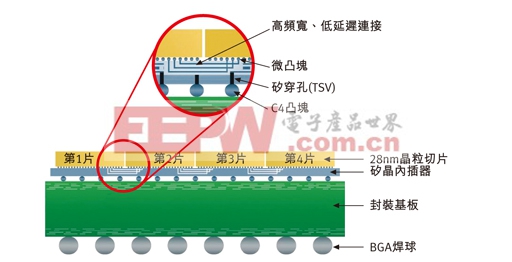

今年秋季則迎來第二個重大的2.5D成功事件,賽靈思公司推出一種使用某封裝工藝的多FPGA解決方案,這種工藝可在硅中介層上互連4個并排且帶微凸塊的Virtex-7FPGA。臺灣的臺積電(TSMC)公司正在生產這種硅中介層,該中介層使用硅通孔技術重新分配FPGA的互連,而硅通孔則匹配使用受控塌陷芯片連接(C4)的基板封裝上的銅球。臺積電公司承諾明年將向其它代工客戶提供其開創性的2.5D至3D轉換技術。

然而,2011年令人驚訝的3DIC發布來自IBM。據IBM公司最近透露,公司正在秘密地大批量生產大眾化移動消費設備使用的成熟3DIC產品,盡管使用的是低密度硅通孔技術。作為收獲的經驗之談,IBM聲稱現在已經認識到3D芯片制造中的遺留工程技術問題,并表示有望在2012年解決這些問題。

“擁有一技之長的年代已經過去。”IBM公司研究副總裁BernardMeyerson表示,“如果您僅依靠材料,或芯片架構,或網絡架構,或軟件和集成,您就可能無法贏得3D性能戰爭。要想打贏這場戰爭,您需要以盡可能最全面的角度使用所有這些資源。”

近期,IBM宣布聯合3M公司并開始研討創建設計師材料——就像是Meyerson描述的尋找“一個真正高的矮人”——這種材料將解決3DIC生產中面臨的最終工程技術問題:過熱。3M的任務是創建一種適合堆疊裸片間使用的底部填充材料,這是一種電氣絕緣材料(像電介質),但導熱性比硅要好(像金屬)。3M公司承諾在兩年內實現這種神奇材料的商用化。

“現在我們正在做試驗,到2013年我們希望開始廣泛的商用。”3M公司電子市場材料事業部技術總監陳明(音譯)表示。

一些分析師不認為IBM-3M聯合研發努力會使他們的產品在3DIC領域中走得比別人更遠。

“3M正在研制的底部填充材料將解決3D堆疊中遇到的散熱問題。”MEMS投資者雜志高級封裝技術首席分析師FrancoisevonTrapp表示,“雖然在大批量生產3DIC之前肯定需要解決遺留下來的一些限制,但我認為任何人都不會相信這是解決3D堆疊遺留問題的終極方案。”

3D無處不在

即使IBM宣稱的領先的3DIC生產技術也不是沒有挑戰者。事實上,TezzaronSemiconductor公司為其鎢硅通孔工藝提供3DIC設計服務已經有多年時間了。Tezzaron的FaStack工藝可以從薄至12微米晶圓上的異質裸片創建3D芯片。這種工藝具有針對堆疊式DRAM的寬I/O特性,而且其亞微米互連密度高達每平方毫米100萬個硅通孔。

去年獲得EETimes年度ACE創新大獎的ZviOr-Bach則認為3DIC設計師需要從硅通過技術過渡到超高密度的單片3D技術。對Or-Bach來說這個觀點一點都不令人奇怪,因為他最近的角色是IP開發公司MonolithIC3DInc的總裁兼首席執行官。而BeSangInc等新創企業聲稱正在制造無硅通孔的單片3D內存芯片原型,并有望于2012年首次亮相。

然而,目前最先進的技術應該是使用硅通孔的3D芯片堆疊,而且每家主要的半導體公司都在研究這種技術。“IBM將這種技術發揮至了極致,并突破傳統思維與3M公司開展合作。然而,IBM公司在3D領域做出的每次進步都將激發三星、Intel和臺積電等競爭對手的創造性,所有這些公司都在獨立開發3DIC技術。”市場觀察人士、TheEnvisioneeringGroup總監RichardDoherty指出。

生產3DIC的技術并不是很新的技術,目前的工作專注于進一步完善。舉例來說,現在許多CMOS成像器使用硅通孔將像素數據從前面帶到基板后面,而堆疊芯片想法本身可以追溯到大約1958年頒發給晶體管先驅WilliamShockley的早期專利。從那以后,業界已經使用了許多堆疊式裸片配置——例如,將MEMS傳感器堆疊在ASIC之上,或將小的DRAM堆疊在處理器內核上——但通常是使用綁定線實現互連。

從綁定線轉變到硅通孔能使互連密度更高,還能幫助設計師脫離矩形的“農場地”框框的束縛,使他們在設計芯片版圖時更像是在設計電路板。沒有電路的區域可以用于其它結構,例如垂直互連總線甚至用于冷空氣的煙道。異質3D堆疊式裸片還能達到新的集成度,因為整個系統可以組合成單個硅塊。

“3DIC帶來的最重要影響是遠離農場式設計的機會,這種農場式設計是將每個芯片分割成相鄰且完全拼接式的矩形塊。”Doherty指出,“與用光芯片上的所有面積不同,3D芯片設計師可以從裸片上切割出方形、三角形和圓形進行垂直互連,并很好地釋放出熱量。”

“3D技術可以給芯片設計帶來許多新的想法。設計師必須采用不同的思維方式,以創新的方式組合他們的CPU、內存和I/O功能,這是每樣東西只能在郵票大小的面積上并排放置的方法所不能做到的。”

有許多半導體協會都在研究制訂3D技術標準。國際半導體設備與材料組織(SEMI)有4個小組專攻3DIC標準。其三維堆疊式集成電路標準委員會包括SEMI成員Globalfoundries、惠普、IBM、Intel三星和UnitedMicroelectronicsCorp.(UMC)以及Amkor、ASE、歐洲的校際微電子中心(IMEC)、亞洲的工業技術研究院(ITRI)、奧林巴斯、高通、Semilab、東京電子和賽靈思公司。

圖1:賽靈思公司組合運用硅通孔和受控塌陷芯片連接焊球在臺積電生產的硅中介層上安裝4個FPGA。(圖片來源:賽靈思)

更多資訊請關注:21ic模擬頻道

評論