一種帶有增益提高技術的高速CMOS運算放大器設計

摘要:設計了一種用于高速ADC中的高速高增益的全差分CMOS運算放大器。主運放采用帶開關電容共模反饋的折疊式共源共柵結構,利用增益提高和三支路電流基準技術實現一個可用于12~14bit精度,100MS/s采樣頻率的高速流水線(Pipelined)ADC的運放。設計基于SMIC0.25μm CMOS工藝,在Cadence環(huán)境下對電路進行Spectre仿真仿真結果表明,在2.5V單電源電壓下驅動2 pF負載時,運放的直流增益可達到124 dB,單位增益帶寬720 MHz,轉換速率高達885 V/μs,達到0.1%的穩(wěn)定精度的建立時間只需4ns,共模抑制比153dB。

關鍵詞:運算放大器;折疊式共源共柵;高速度;增益提高;三支路電流基準

隨著當今集成電路技術遵從摩爾定律的快速發(fā)展,在深亞微米級甚至納米級工藝下電源電壓及MOS管特征尺寸不斷降低,器件的諸多性能已達到瓶頸。因此,各種高性能模擬或混合集成電路如∑-△調制器、開關電容濾波器和流水線A/D轉換器中的高性能運算放大器的研究已成為當今的熱點。速度和精度是模擬集成電路中均很重要的性能指標,前者需要器件有大的帶寬,短溝道以及單極點系統(tǒng)設計;后者則需要在小偏置電流、長溝道、多級放大器設計的同時實現高增益。因此兩者的實現必然會產生設計上的沖突,而這種矛盾也激勵著電路設計師去根據應用的需要的同時折中考慮并且創(chuàng)新電路結構來滿足系統(tǒng)的要求。

1 電路的選擇

1.1 主運放的選擇

高速運算放大器作為Pipelined ADC中的一個重要模塊,它的特性直接決定了電路系統(tǒng)的整體性能,對于作為ADC前置放大器的設計,運放要有大的單位增益帶寬和高的開環(huán)增益;同時,要兼顧功耗以及輸出擺幅、共模抑制比(CMRR)等參數的考慮。共源共柵結構能夠對速度和精度有很好的折中,已廣泛應用于運算放大器、基準源和濾波器等模擬器件中,它總的劃分有兩種結構:套筒式共源共柵結構(telescopic-cascode)和折疊式共源共柵結構(fold-cascode)。

套簡式共源共柵運放只有兩條支路組成,功耗較小,且由于次主節(jié)點附近的寄生電容較小,所以帶寬更大,速度更快,但該電路由于是由多級管層疊而成,共模輸入范圍和輸出擺幅過小,如果不接二級電路很難在低壓下正常工作;折疊式共源共柵運放的次主極點周圍的寄生電容較大,頻率特性相對于套簡式共源共柵結構較差但差距不大,由于結構呈折疊狀而省去了層疊的多層管,其共模輸入范圍及輸出擺幅均遠大于套簡式共源共柵的對應值,但其結構為4條回路,故其功耗略大。

根據實際需要從應用角度考慮,作為ADC前置放大器,所設計的運放要求要在能保證精度基礎上有盡可能快的速度。上述分析表明,兩種基本的共源共柵結構所構成的運放均有較高的速度,但是相對而言折疊式共源共柵比套筒式共源共柵有更大的共模輸入范圍和輸出擺幅,且其輸入輸出可以短接而且輸入共模電平更容易選取,因此折疊是共源共柵運放更符合要求。

1.2 增益提高(gain boosting)技術

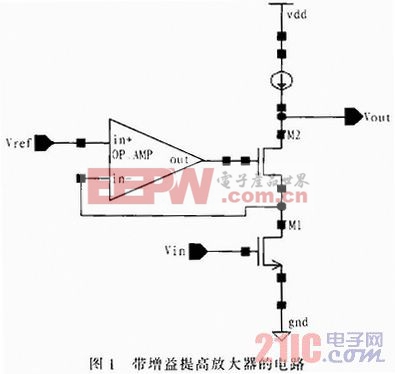

在深亞微米及納米級工藝水平下MOS管最小溝道長度越來越小,器件的帶寬越來越大從而速度越來越快,但增益卻越來越低,單級共源共柵運放的增益也降至約40dB左右,這樣的結構很難滿足對精度的基本要求,故本設計增加了增益提高級。其基本原理如圖1所示;將M1看成一個反饋電阻,與M2構成一個從電流到電壓的負反饋環(huán)路,通過減小由輸出到輸入管漏極的反饋,使得M1的漏電壓隨輸出電壓的變化很小,流過M1的電流更加穩(wěn)定,因而產生了更高的輸出阻抗。設輔助運放Aadd放大倍數為A,則輸出阻抗為:

Rout=(gm2ro2(A+1)+1)ro1+ro2 (1)

其中,ro1、ro2分別是M1、M2管得小信號等效電阻,gm2是M2的跨導。可見利用增益增強技術可以是輸出電阻提高A倍,從而也使得電路的直流增益增大了A倍:

Alot=gmiro1(gm2ro2(A+1)+1) (2)

但增益增強技術在提高增益的同時也帶來一個明顯的缺點:在圖1電路中得輸出端和M1的漏端分別形成運放的主極點和次主極點。因此經常會在輔助運放的單位增益帶寬附近產生零極點對,盡管不會影響運放的頻率響應,但它卻使運放的建立特性變差。通常的處理方法是提高零極點對的發(fā)生頻率,即提高輔助運放的單位增益帶寬,但若將輔助運放的單位增益帶寬頻率提高到主運放的第二極點附近時,整個運放將不穩(wěn)定。因此,通過分析得出使輔助運放Aackl的單位增益帶寬要介于運放閉環(huán)-3 dB帶寬和主運放的非主極點值之間,并在輔助運放輸出端和地之間增加補償電容C0和C1進行微調即可,其大小約為負載電容的1/2~1/3。

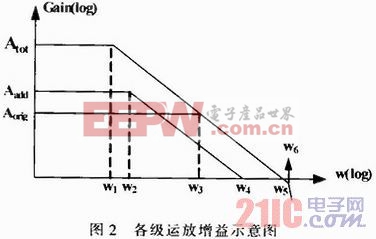

圖2是各級運放的增益帶寬關系示意圖。Aorig為未加增益輔助運放的增益曲線,Aackl為輔助運放增益曲線,Alot為添加輔助運放后主運放的增益曲線。若要使系統(tǒng)穩(wěn)定,則需:

w3w4w6 (3)

評論