一種數模信號轉換的實際案例介紹(一)

振動、溫度、壓力和光等現實世界的信號需要精確的信號調理和信號轉換,然后才能在數字域中進行進一步數據處理。

本文引用地址:http://www.j9360.com/article/186060.htm為了克服當前高精度應用的多種挑戰,需要一個精心設計的低噪聲模擬前端來實現最佳信噪比(SNR)。許多系統既負擔不起最昂貴的器件,也無法承受低噪聲器件的更高功耗。

本文提出了一種系統的方法來設計一個增益模塊和ADC組合,并給出一個支持此方法的實例。在調理低頻(接近dc)信號時,該電路進行噪聲計算和分析。

設計模擬前端時,請遵循以下七個步驟:

1) 描述傳感器或增益模塊前部的電氣輸出

2) 計算ADC的需求

3) 為信號轉換找到最佳ADC + 基準電壓

4) 為運算放大器找到最大增益并定義搜索條件

5) 找到最佳放大器并設計增益模塊

6) 根據設計目標檢查解決方案總噪聲

7) 運行模擬并驗證

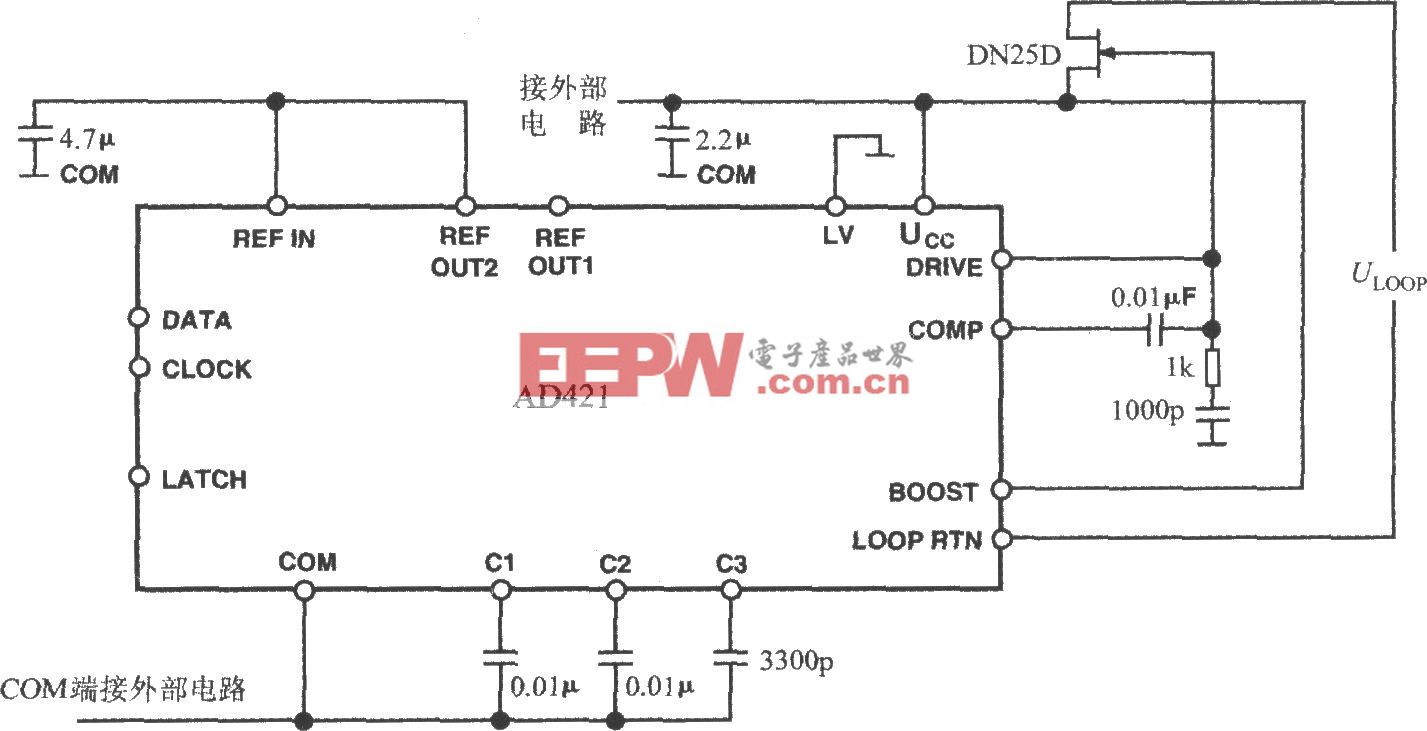

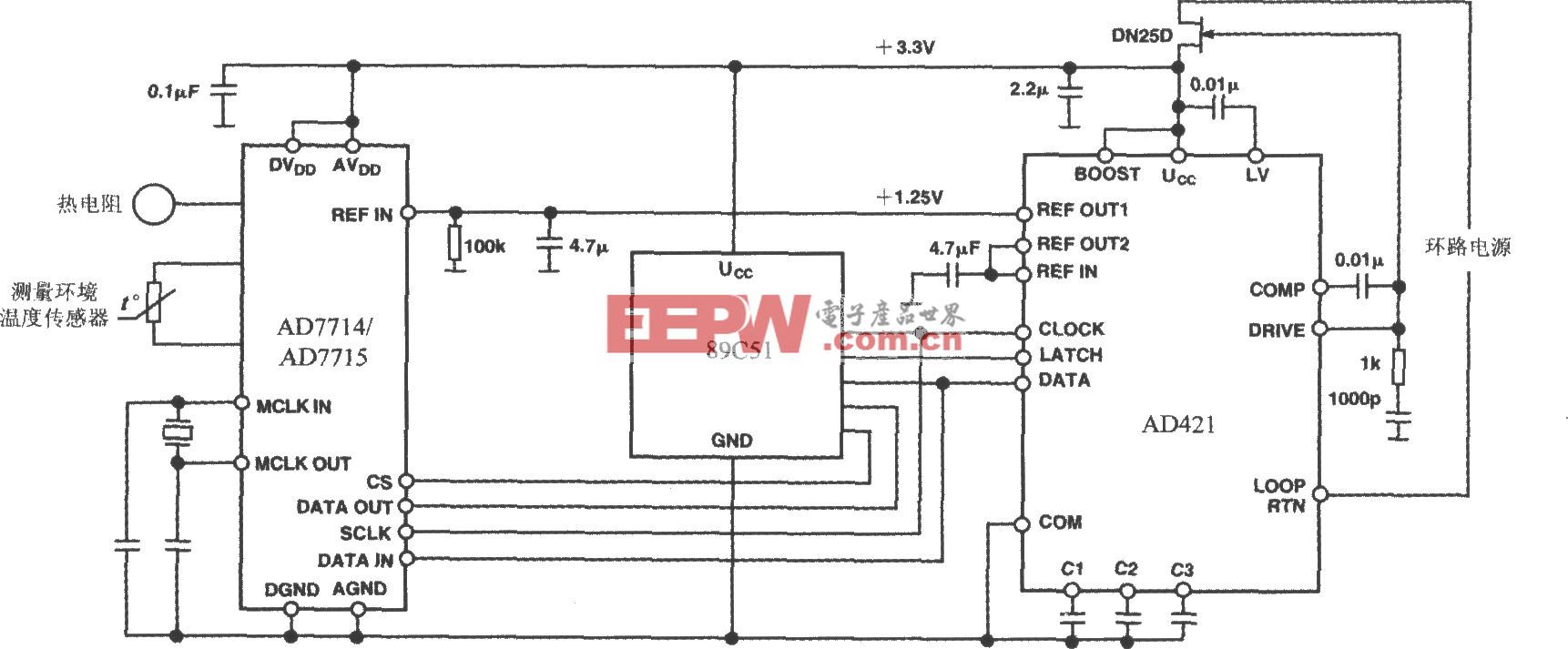

圖1 典型信號調理鏈

第1步:描述傳感器或增益模塊前部的電氣輸出

信號可能直接來源于傳感器,也可能在到達增益模塊之前經過EMI和RFI濾波器。為了設計增益模塊,必須知道信號的ac和dc特性以及可用的電源。知道了信號的特性和噪聲電平后,我們就能知道選擇ADC時需要何種輸入電壓范圍和噪聲電平。

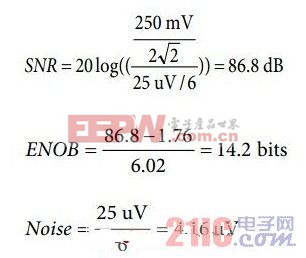

假設有一個傳感器,以250 mV p-p(88.2 mV rms)和25 μV p-p噪聲的滿量程幅度輸出一個10kHz信號。我們進一步假設系統中有一個可用的5V電源。有了這些信息,我們應該能計算出第2步中的ADC輸入端的信噪比。為簡化數據處理和避免混淆,假設我們將該解決方案設計為在室溫下工作。

第2步:計算ADC的需求

我們需要何種ADC、采樣速率如何、多少位、噪聲指標如何?若從第一步知道了輸入信號幅度以及噪聲信息,我們就能計算出增益模塊輸入端的信噪比(SNR)。我們需要選擇一個有更佳信噪比的ADC。在選擇ADC時,知道SNR將有助于我們計算有效位數(ENOB)。此關系表達式如下。

理想的ADC數據手冊總會標出SNR和ENOB。此例中所需要的86.8 dB SNR和14.2位ENOB決定了我們應選擇一個16位的模數轉換器。此外,奈奎斯特準則要求采樣率(fs)應至少兩倍于最大輸入頻率(fin),因此一個20-kSPS ADC應該就已足夠。下一步我們需要設計總體解決方案,使得噪聲密度不超過416 nV/rt-Hz。

第3步:為信號轉換找到最佳ADC+基準電壓

有了一系列的搜索條件,我們就有許多種方法找到合適的ADC。要找到一個16位ADC,最簡單的方法之一就是使用廠商網站上的搜索工具。輸入分辨率與采樣速率,就可找到許多推薦的ADC。

許多16位的ADC滿足14.5位ENOB需求。如果您想得到更佳的噪聲性能,可使用過采樣迫使ENOB達到16位(由4^n過采樣得到n位增強)。通過過采樣,您可以使用較低分辨率的ADC:256過采樣的12位ADC(4^4過采樣)可得到16位噪聲性能。

圖2 典型的ADC選型表

在我們的例子中,這意味著5.126 MHz采樣率的12位ADC(20 kSPS × 256),或是4^2過采樣的14位ADC;若1.28 MSPS則更佳。然而這些選擇的成本卻和AD7685(16位、250 kSPS ADC)相當。

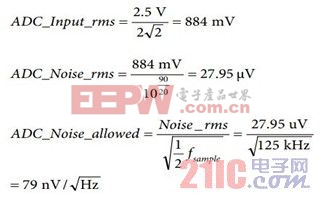

從列表中我們選擇了AD7685(16位PulSAR ADC)。該轉換器具有90-dB SNR和250 ksps采樣率,符合我們的需要。此ADC推薦搭配使用ADR421/ADR431精密XFET基準電壓源。2.5-V的輸入范圍超過了我們需要的250-mV p-p輸入特性

AD7685參考輸入具有動態輸入阻抗,因此需進行去耦以使寄生電感最小(方法是在引腳附近放置一個陶瓷去耦電容,并用較寬的低阻抗走線進行連接)。一個22 μF陶瓷芯片電容可提供最佳性能。

相關文章推薦:

評論