電力線載波擴頻通信調制模塊的設計

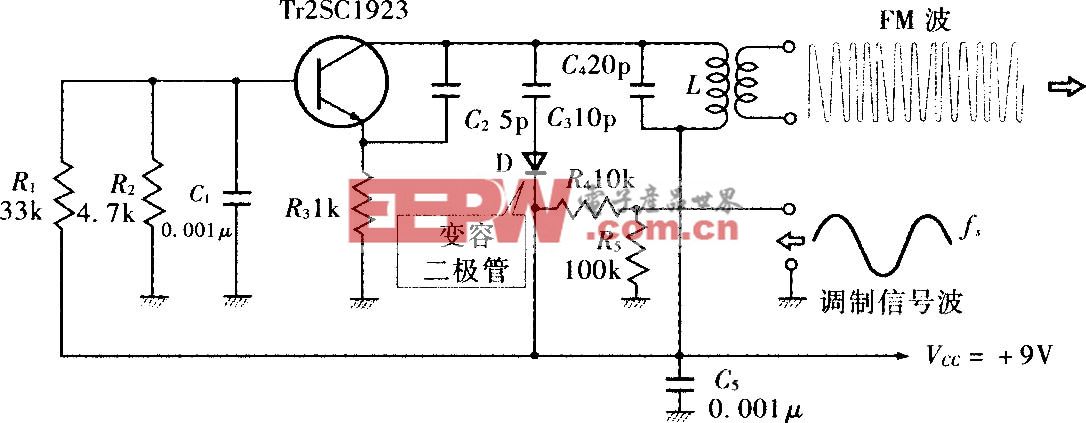

通常擴頻通信系統的解調電路很復雜,本系統為了使解調電路簡單化,采取基帶信號速率與擴頻碼元周期同步同速的特殊措施,省去了解調電路中復雜的載波恢復電路。直接序列擴頻通信系統中,接收端與發送端必須實現載波同步、PN碼同步,才可以正常工作。同步系統是擴頻通信的關鍵技術。

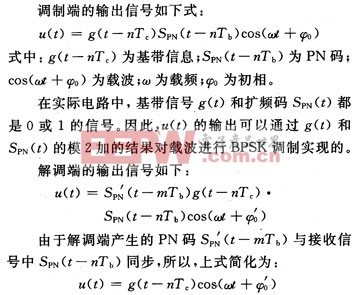

1 本擴頻系統的調頻解調原理

本系統的載波,PN碼和基帶信號的速率來自于同一個時鐘源,而且載波頻率和PN碼頻率都是基帶信號速率的整數倍,所以系統在解調端獲得PN碼同步的同時,也獲得了載波的同步。

2 系統總體設計及參數選擇

本系統設計其頂層采用圖形設計方式,各模塊基于Verilog HDL設計。圖1為系統模塊圖。

基帶數據的碼速率為0.806 Kb/s,PN碼速率為25 Kb/s,基帶信號與PN碼相異或輸出信號去調制載波產生BPSK信號,載波的中心頻率為100 kHz。本系統調制電路各部分的時鐘源參數依據系統框圖選擇,晶振頻率是50 MHz,以上各部分的時鐘經分頻后得到。

3 模塊設計及實現

3.1 分頻模塊

本系統發射的基帶數據速率是0.806 Kb/s,PN碼的頻率是25 kHz,正弦波的頻率是100 kHz,所以整個系統所需的時鐘為50 MHz,PN碼所需的時鐘是25 kHz,基帶信號所需的時鐘是0.806 Kb/s。為了更好地實現同步,后面兩者分別經過16×125分頻,31×16×125分頻得到,分頻器通過編程實現。時序仿真如圖2所示。

3.2 PN碼發生器模塊

采用最大長度線性反饋移位寄存器(m序列)生成擴頻碼字,其本原多項式如下:

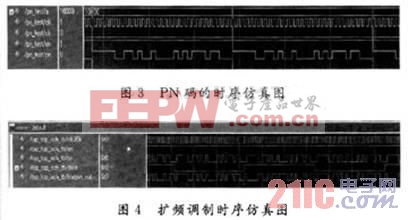

PN發生器的時序仿真如圖3。產生的25-1位PN碼為:

[ 1 1 1 1 1 0 0 1 1 0 1 0 0 1 0 0 0 0 1 0 1 0 1 1 1 0 1 1 0 0 0 ]

3.3 直接序列擴頻模塊

直接序列擴頻的實現比較簡單,用PN碼與信息序列模二相加(波形相乘),對基帶信息進行擴頻調制。本設計采用31位的PN碼,需要滿足如下關系Tc=31Tb(Tc為基帶信號周期;Tb為PN碼周期)。擴頻調制的時序仿真如圖4所示。

3.4 BPSK調制模塊

本系統數字正弦發生器采用了直接數字頻率合成(DDS)技術。DDS由相位累加器、相位加法器、波形存儲器(ROM)組成。其中,ROM中存放經過采樣、量化處理后的周期連續信號一個周期波形的幅度值。在具體實現中ROM表采用了10位,即1 024個采樣點。利用DDS產生100 kHz的載波,對擴頻信號進行調制。

因此,在本設計中,BPSK的調制通過對擴頻模塊產生的序列對兩路相移為180°的正弦波進行選通來調制,在前面利用DDS產生了兩個正弦波的ROM表,通過擴頻序列對兩張表的數據進行選通,則所輸出波形能夠實現BPSK調制。

在本設計中,擴頻信號與BPSK調制信號的對應關系為:“1”對應180°;“0”對應0°。所以,當數據為1時,選擇正弦波的初始相位為180°;當數據是0時,選擇正弦波的初始相位是0°,這是通過Verilog編程實現的。

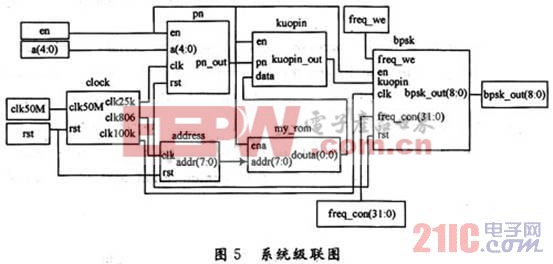

4 系統聯合仿真

對各個子模塊設計仿真完之后,把各個模塊進行級聯仿真調試。頂層模塊采用原理圖輸入法,該方法具有直觀清晰的特點。系統級聯圖如圖5所示。

系統級聯的時序仿真如圖6所示。

5 結語

在FPGA芯片上實現了直接序列擴頻發射系統,由于所有模塊都集成在一個芯片中,提高了系統的穩定性和可靠性。且由于FPGA是一個完全的硬件構架,其中的電路全部由與非門實現,比用傳統的擴頻系統處理速度更快,并且系統可以通過編程來修改升級,具有很大的靈活性。最后,因載波頻率和PN碼頻率都是基帶信號速率的整數倍,所以,系統在解調端獲得PN碼同步的同時,載波也獲得了同步,這樣就大大降低了后端解調器的復雜度,具有實用價值。

更多資訊請關注:21ic模擬頻道

評論