使用儀表放大器的高性能加法器

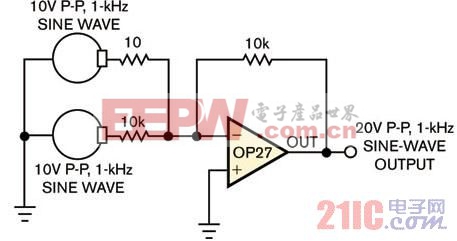

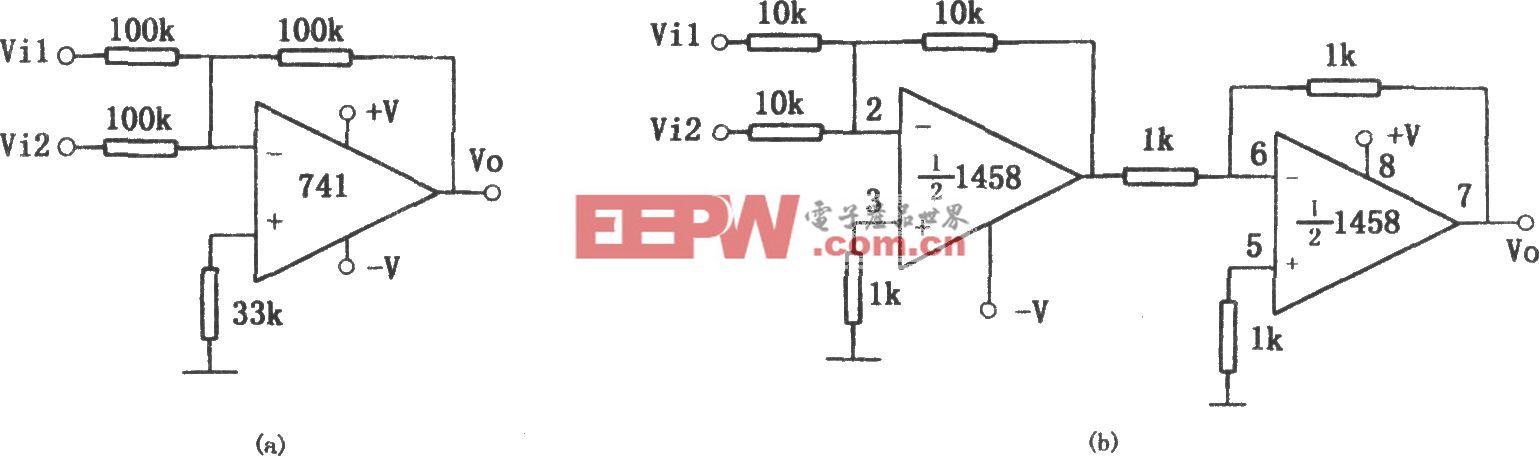

隨著儀表放大器價格的逐步下滑,它們可以為傳統上采用運算放大器的應用提供更高的性能。圖1中的運放加法器有一些缺點。首先,輸入端為中低輸入阻抗,這是由每個信號的輸入電阻所決定的。當驅動信號源阻抗較大,或需要設計低阻驅動源時,這種結構會產生增益誤差。另外,電路也沒有共模抑制能力,因此輸入端必須是單端的。最大增益的通道限制了整個系統的性能。一個通道的較高增益會產生較低帶寬、較大失真,并增加系統所有通道上的噪聲。為限制這些作用,即使低性能的加法器也需要高性能、大帶寬的運放。

本文引用地址:http://www.j9360.com/article/185890.htm

圖1,一種采用單運放的典型加法器結構。

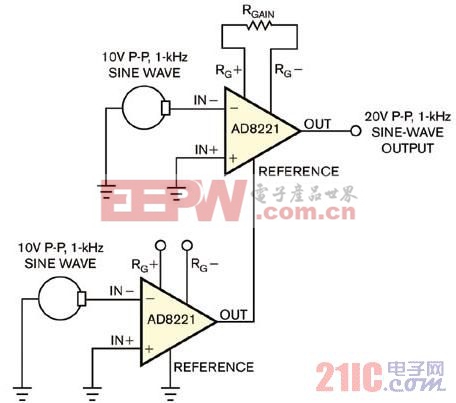

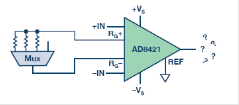

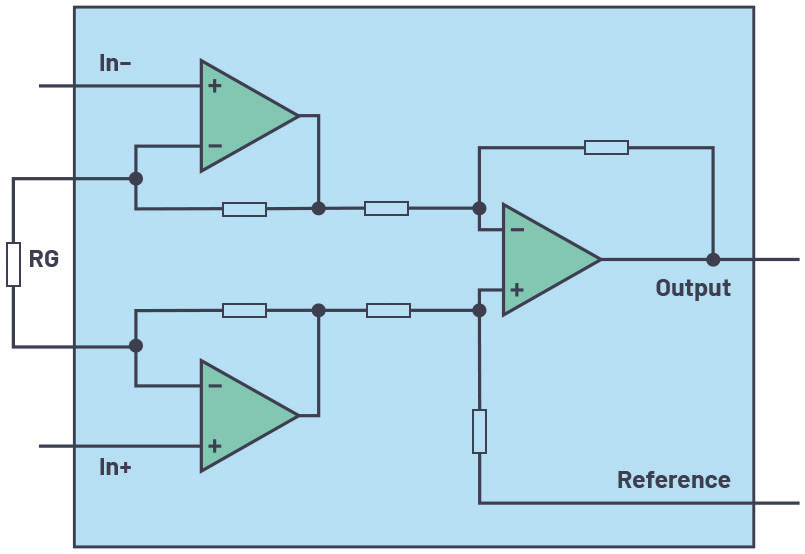

這款運放加法器的噪聲增益為1+10,000/(10||10,000)。最高增益的輸入信號以及10Ω阻抗決定了噪聲增益,但所有的輸入緩沖器都增加了偏移電壓、增益誤差、噪聲與失真。你可以用儀表放大器增加輸入阻抗,提高共模抑制能力。一只儀表放大器的輸出電壓與正、負輸入端之間的壓差成正比。在RG腳連接一只電阻RGAIN,就可將此信號放大(圖2)。輸出電壓產生于參考腳與輸出腳之間。這種結構可以用參考腳將一個加法器結構中的多個信號級聯起來。每個儀表放大器的增益可以設定為不同值。

圖2,兩只儀表放大器為該加法器電路提供了更多的輸入阻抗。

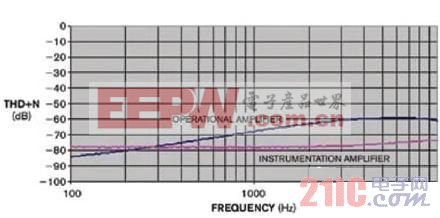

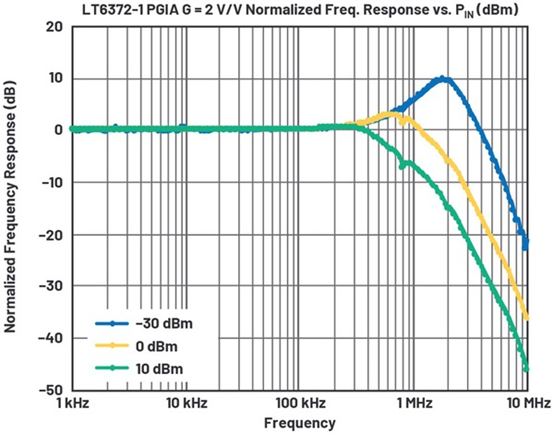

圖3,在高于300 Hz頻率下,儀表放大器結構表現出更強的THD+N性能。

本系統比簡單的運放加法器有多個優點。例如,每個輸入端都有極高的輸入阻抗,并有獨立的共模抑制能力,它由連接到該通道上的儀表運放所決定。通道增益越高,則共模抑制越大,得到的誤差越小。還可以使用儀表放大器的反相與非反相端,方便地加減信號;如果愿意,該放大器也可以使用差分輸入信號。此外,每個信號的失真、噪聲增益和帶寬都與其它信號無關,從而有較低的偏移電壓、增益誤差、噪聲和失真。圖3的THD+N(總諧波失真加噪聲)圖表明,儀表放大器加法器的失真為運放加法器的五分之一,哪怕所用儀表放大器的帶寬為1MHZ,并工作在1mA,而運放帶寬為8 MHz,工作在4.5mA。

更多資訊請關注:21ic模擬頻道

評論