數字電路中△I噪聲的危害分析

隨著數字電路向高集成度、高性能、高速度、低工作電壓、低功耗等方向發展,數字電路中的△I噪聲的特性和抑制△I噪聲的技術成為一個亟待系統、深入研究的領域。

本文引用地址:http://www.j9360.com/article/185811.htm△I噪聲的產生過程及其基本特點表明[1,2]:△I噪聲是由數字電路的電路結構和工作過程決定的,恰當的電路設計只能在一定程度上減小(而不可能消除)△I噪聲。△I噪聲是數字電路固有的。數字電路中不同單元產生的△I噪聲會發生疊加,電路的規模越大,疊加出現的可能性越大,造成的電流尖峰脈沖越強;△I噪聲是寬帶噪聲源,頻譜寬度主要由電路的速度決定,速度越高,頻譜范圍越寬;△I噪聲同時產生傳導騷擾和輻射騷擾,電路的速度越高,輻射發射越強。

本文在△I噪聲的產生過程及其基本特點的基礎上,研究△I噪聲的主要危害。

1電源電壓波動

1.1寄生電阻引起的電源電壓波動

數字IC內部和數字系統中都有電源分配網絡。電源分配網絡的導線都有寄生電阻。電源電流尖峰脈沖(△I噪聲)通過電源分配網絡時,會產生歐姆電壓降。從而引起電源電壓波動。

對數字IC內部的電源分配網絡,以目前流行的“Vanilla” 0.25μm CMOS工藝為例,考慮一條長2cm的電源線(VDD)或地線(IC內部互連線),其上每1μm寬度的電流為1mA。這一電流密度接近于一條鋁線所能承受電流的最大值,原因是電遷移(electronmigration)的影響[3]。該導線(1μm寬度)的電阻為1kΩ。一個1mA/μm的電流將導致1V的電壓降。這一電源電壓波動將降低噪聲容限,并使電路各點的邏輯電平與離開電源端的距離有關。

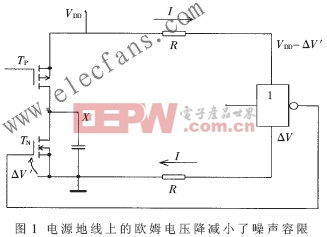

如圖1所示,把一個離電源引線和地引線都很遠的反相器連接到一個接近電源的器件上。由于電源地線上的電壓降IR(歐姆電壓降)引起的邏輯電平差可能使晶體管TN部分導通,可能引起一個預充電的節點X意外放電。如果連接的門是靜態的,則有可能引起靜態功耗。

總之,來自片上邏輯電路和存儲器及輸入/輸出(I/O)引線上的電流脈沖會造成電源分配網絡上產生電壓降,這是片上電源噪聲的主要來源。除了造成可靠性降低的風險外,電源網絡的歐姆電壓降也會影響系統的性能,因為電源電壓的一個很小的下降都可能造成延時的明顯增加。

無論是數字IC內部的電源分配網絡的導線(目前多用鋁),還是數字系統中的電源分配網絡的導線(一般用銅),都存在趨膚效應(skin effect)。趨膚效應使導線的有效導電截面積隨信號頻率的升高而減小,使導線的電阻隨信號頻率的升高而增大(

)[4,5]。

由于△I噪聲是寬帶噪聲源,所以趨膚效應會使電源分配導線的電阻顯著變大(相對于直流電阻),進而使歐姆電壓降顯著變大。

1.2 寄生電感引起的電源電壓波動

電源分配網絡還有寄生電感,數字IC的電源地線也有寄生電感。

電源電流尖峰脈沖(△I噪聲)通過電感時,會產生感應電壓,從而引起電源電壓波動。

單個TTL反相器引起的電源電流尖峰脈沖最小值約為30mA[1,2],設門電路的狀態轉換時間為2ns,設電源地線的寄生電感L=500nH,則引起的電源電壓波動為:

這樣高的尖峰脈沖電壓通過邏輯器件之間的驅動線耦合到其他邏輯器件的輸入端,幅值很可能超過TTL系列輸入低電平的上限值0.8V,從而造成邏輯電路的誤動作。

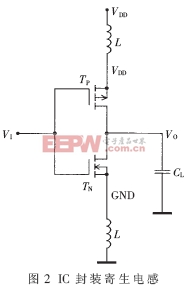

CMOS數字IC中電源電流尖峰脈沖(△I噪聲)經封裝寄生電感引起的電源電壓波動如圖2所示。圖中電路是數字IC輸出壓焊塊驅動器(output pad driver)的最后一級,它驅動一個10pF的負載電容,電壓擺幅(voltage swing)為2.5V。反相器的尺寸設計成使輸出信號的上升時間和下降時間(tr和tf)等于1ns。由于電源和接地線是通過電源引線連到外部電源上的,所以兩根連線都具有一個寄生串聯電感L。對于傳統的穿孔(through-hole)封裝技術,其電感一般為2.5nH左右。為簡化分析,假設反相器的作用像一個電流源,以不變的電流充(放)電負載電容。為達到1ns的輸出上升時間和下降時間,所需要的平均電流為:

Iav=[10pF×(0.9-0.1)×2.5V]/1ns=20mA

當這一情形發生在緩沖器輸入端并由一個很陡的階躍函數來驅動時,若tf=50ns,則仿真得到突變的電流變化可在寄生電感上引起高達0.95V的尖峰電壓。事實上,如果這一電壓降本身不能使翻轉變慢和降低對電流的要求,它的值會更大。然而,如此大的電源電壓波動是不能允許的。

在一個實際的電路中,單個電源引線常常用于許多門或輸出驅動器。這些驅動器同時切換會引起更為嚴重的瞬態電流和電壓降。結果,內部電源電壓與外部電源電壓有相當大的偏差。例如,如果一條輸出總線的16個輸出驅動器的電源線都連到同一條封裝引線上,則它們同時切換時會引起至少1.1V的電壓降。

評論