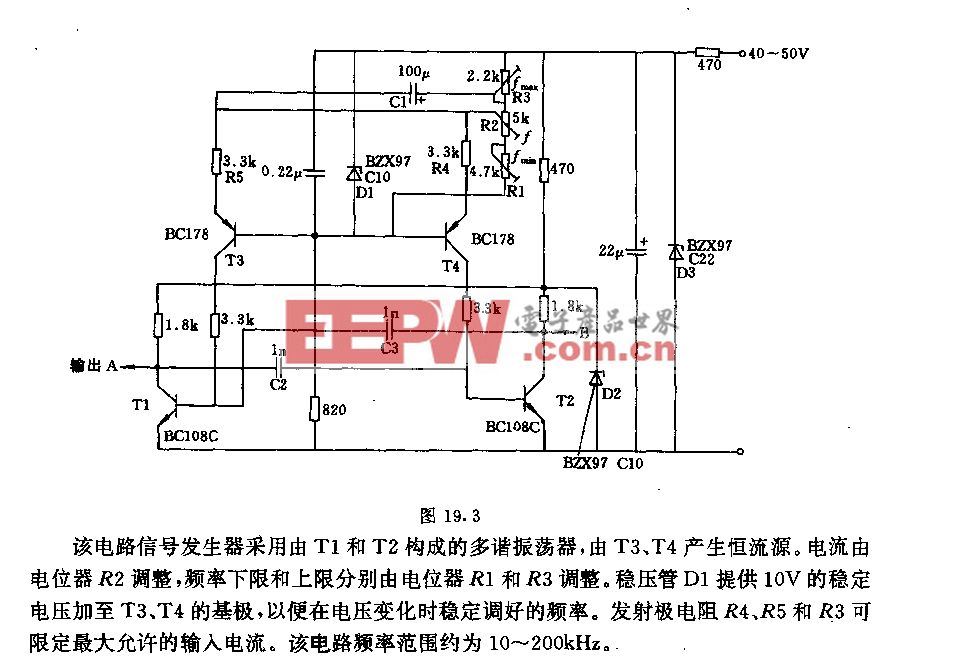

電磁無損檢測中信號發生器的設計與實現

摘要:在電磁無損檢測系統中,信號頻率及其穩定性對檢測效果影響很大,為了解決該難題,文中給出了一種應用DDS技術設計的新型信號發生器解決方案。該信號發生器具有頻率精度高、穩定性好、分辨率高的特點,有利于提高電磁無損檢測的效果。

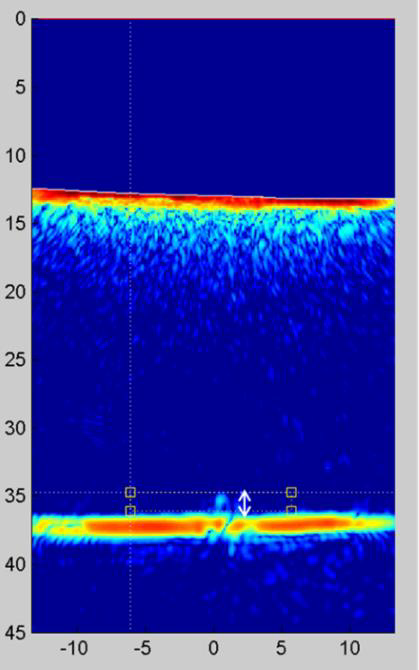

電磁無損檢測(如渦流)是基于電磁感應原理的無損檢測技術。當載有交變電流的檢測線圈靠近導體時,由于交變電流在周圍空間中會產生交變磁場,因而在被測試件(導體)表面產生趨膚效應并感應出交變電流。通過優化設計可使被測試件表面電流達到均勻分布,從而使周圍磁場也達到均勻,而當被測試件表面有缺陷時,電流就會發生畸變,均勻磁場隨之發生變化,這樣,直接或間接測量出該磁場的變化,就能檢測試件的缺陷。雖然人們在電磁無損檢測方面已取得了許多進展,但仍有許多不盡人意之處,其中一個重要的因素便是檢測系統信號的穩定性,這一點對測量結果會產生嚴重的影響。因為信號發生電路是整個檢測系統的信號源,它的信號頻率是否穩定將對整個檢測系統的工作起十分關鍵的作用,信號頻率不穩定會給信號的后續處理帶來極大的困難,甚至使電磁檢測難以進行。為了解決上述問題,筆者應用DDS技術設計了一個高穩定性信號發生器。

1 DDS的工作原理

直接數字合成(DDS-Direct Digital Synthesizer)是近幾年發展起來的一種新的頻率/波形合成技術。該技術具有頻率分辨率高、轉換速度快、信號純度高、相位可控、輸出信號無電流脈沖疊加、輸出可平穩過渡且相位保持連續變化等優點。近年來在通訊、雷達、GPS、蜂窩基站、圖像處理及HDTV等領域得到了廣泛應用。

該技術是根據奈奎斯特取樣定理,從連續信號的相位Φ出發,對一個正弦信號進行取樣、量化、編碼,然后將形成的正弦函數表存入ROM/RAM中,合成時則通過改變相位累加器的頻率控制字來改變相位增量,相位增量不同將導致一個周期內取樣點數的不同。因角頻率ω=△φ△t,故可在取樣頻率不變的情況下,通過改變相位累加器頻率控制字的方法將這種變化的相位/幅值量化為數字信號,然后通過 D/A變換和低通濾波即可得到相位變化的合成模擬信號頻率。

圖2

圖1是DDS的基本原理框圖,它主要由四部分組成,第一部分為相位累加器,用于決定輸出信號頻率的范圍和精度;第二部分為正弦函數功能表(波形存儲器),用于存儲經量化和離散后的正弦函數的幅值;第三部分為D/A轉換,可產生所需的模擬信號;第四部分為低通濾波,用來減少量化噪聲、消除波形尖峰。參考頻率源是一個高穩定度的晶體振蕩器,用以同步 DDS中各部件的工作,因此,DDS輸出的合成信號的頻率穩定度和晶體振蕩器是一樣的。從原理上還可看出,它是用高穩定的固定時鐘頻率來對所要合成的信號進行相位取樣的,單位時間內取樣量越大,則合成的頻率越低。取樣量的大小由可程控的頻率設定數據決定。

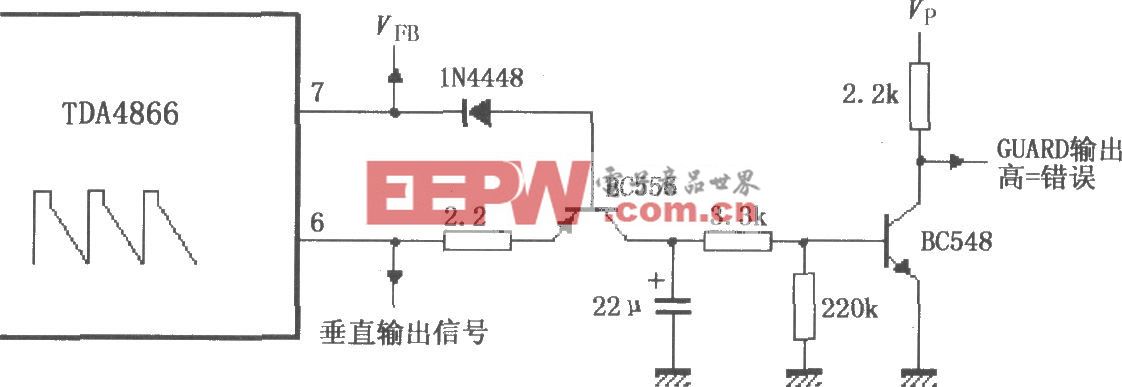

2 DDS芯片AD7008的結構原理

AD7008為單片DDS集成芯片,其結構如圖2所示。該器件內含32位相位累加器、正余弦查找表及10位DAC的DDS調制器,時鐘頻率可達20~50MHz;還內含兩個10位乘法器、20位IQMOD寄存器及12位相位寄存器。除了可合成正弦波外,還可實現調頻、調相、調幅及數字解調,同時提供了可與微機接口的并行和串行接口。

由于AD7008的相位累加器為32位,故2π=232,則△phase必須在0≤△phase≤232-1的范圍內,每一時鐘周期,32位累加器累加一個相位階距,輸出頻率fout為:

fout=△phasefclock/2 32

式中,fclock是參考頻率。實際使用中,fout的上限取fclock的40%(考慮到相位噪聲和雜散信號干擾 )?即△phase上限取0.4232。△phase可通過控制FSE-LECT從FREQ0、FREQ1中選擇。盡管AD7008包含有32位相位累加器,但其輸出僅為12位,因此沒有必要也不可能用32位的分辨率。12位的相位數據經查詢可轉換成10位幅度信號。如果不要求調幅,IQ乘法器可以被旁路(CR2=0),而將正弦信號幅值直接送往DAC電路。通過外電阻Rset可對DAC滿量程輸出電流進行調節,公式如下:

Iout(mA)=6233Vref(V)/Rset(Ω)

圖4

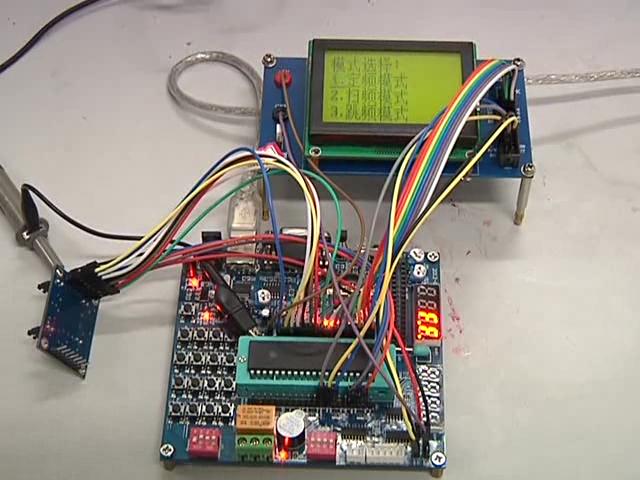

3 軟硬件實現

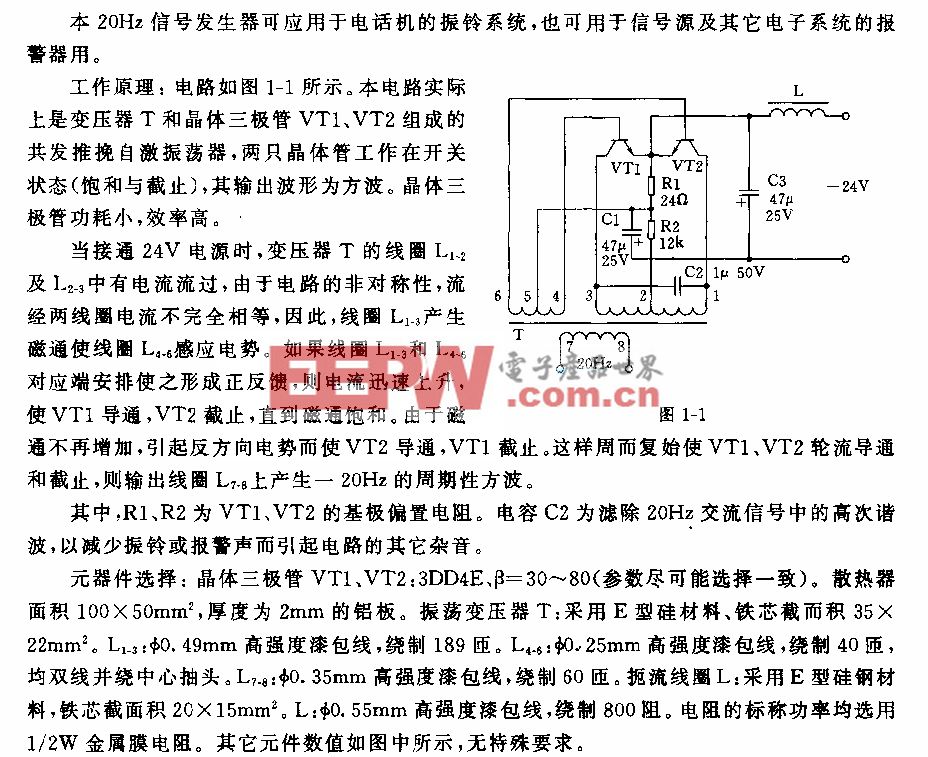

應用DDS技術設計的信號發生器的原理框圖如圖3。它主要由單片機89C52、DDS芯片AD7008AP20、6階橢圓低通濾波器、乘法型D/A轉換器AD7524、功率放大電路以及正交信號形成電路組成。該信號發生器的工作過程如下:

(1)對AD7008芯片初始化,選擇總線方式;

(2)通過鍵盤或上位PC機的串口輸入信號頻率和幅值;

(3)用單片機計算并得到頻率和幅值的控制字,然后通過AD7008的MPU接口裝入32位并行寄存器中,并行寄存器中命令數據在裝載指令(LOAD)及命令信號 (TC0~TC3)的作用下裝入相應的寄存器中,DDS開始工作。

(4)幅值調整。通過控制AD7524來改變AD7008的10位數模轉換器參考電壓,以實現輸出幅值控制。

89C52和AD7008的接口電路如圖4所示。圖中?89C52的P0口和AD7008的D0~D7相連。由于89C52是8位單片機,故AD7008的D8~D15接地。同時,P0.0~P0.3和AD7008的TC0~TC3相連。用3-8譯碼器決定數據傳送到數據總線還是傳送到控制總線。P1.0可用來控制AD7008的復位。20MHz的有源晶振可為AD7008提供時鐘。D/A轉換器AD7524和AD7008的FS ADJ相連,可用于控制滿量程輸出幅度。由于AD7008是電流輸出,輸出阻抗為50Ω,因此電路中設計了電流電壓轉換器,用以實現電流/電壓轉換。

3.2 橢圓低通濾波器設計

AD7008輸出端有一個10位的D/A變換器。由于輸出的合成信號是階梯狀的,帶有很豐富的高次頻譜分量,因此必須將它們濾除,以得到頻譜純凈的正弦波輸出。通常要求濾波器的衰減特性要陡直,延遲時間要短。在常用的巴特沃斯、切比雪夫和橢圓濾波器中,橢圓濾波器以其良好的通帶和阻帶特性受到偏愛,因此,本系統在設計時采用6階橢圓低通濾波器。

本設計從直流到5MHz處的最大波紋為0.25dB,在5.5MHz處最小衰減為60dB,Rs=Rl=900Ω,圖5是根據橢圓函數低通濾波器的設計方法設計的濾波器電路及Matlab仿真波形。

AD7008的輸出信號一路經功率放大后輸出,另一路信號作為參考信號經方波轉換電路形成方波。然后通過正交信號形成電路即可獲得兩個正交的方波信號以作為電磁無損檢測信號的參考信號輸入。該電路由集成鎖相環4046和兩片74F74組成,其原理圖如圖6所示。鎖相環是一個相位自動跟蹤的負反饋系統。鑒相器可將輸入和輸出反饋信號的相位差轉換成脈沖寬度信號,并經低通濾波器平滑后產生直流電壓信號去控制壓控振蕩器,以使輸入和輸出準確同頻同相。

3.4 軟件實現

該系統的軟件設計主要由三個部分組成:LCD驅動程序、鍵盤輸入處理程序、AD7008驅動程序。系統的總體軟件流程圖如圖7所示。

4 結束語

結合DDS技術和單片機控制技術設計的信號發生器硬件結構簡單,編程控制也比較方便。和傳統的模擬信號發生器相比,該信號發生器頻率精度高、相位精確可控、硬件簡單。因此在許多對信號頻率穩定性和分辨率要求較高的場合得到廣泛的應用。

------------

評論