貫穿整個IC實現流程的集成化低功耗設計技術

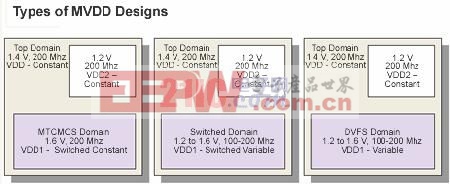

其中一項標準技術是將設計分為大量“電壓島”(圖2)。雖然供電電壓較低的電壓島,其性能也就較差,但其動態功耗也將大幅降低。

圖2. 多電壓域(multi-Vdd)設計類型。

在將設計分為多個電壓島時,信號從一個電壓域到另一個電壓域傳輸必須要插入適當的電壓轉換器或隔離元件。一個真正有功耗意識的設計環境應該能夠自動插入這些單元并做好其驗證工作。

由電壓島和降頻技術所組成的動態電壓和頻率縮放(DVFS)是最先進的一種降低動態功耗方式。系統可被設計為各個功能塊按照不同的電壓和頻率組合工作,隨著器件的操作模式變化而變化。這就是為什么多核處理器能具有長待機的電池壽命和高效的按需計算能力的原因。

靜態功耗

在當今的工藝技術中,不工作時元器件的漏電流是個大問題。這種電流與溫度和開關閾值成指數關系,給功耗優化工作帶來了很大困難。

解決靜態漏電問題的一種方式采用具備多閾值電壓(Vt)元器件的庫,在設計中一部分使用低閾值晶體管,其它部分則使用高閾值晶體管,不過這只能解決部分問題。其中低閾值晶體管開關速度較快但漏電流較高、功耗較大;而高閾值晶體則開關速度較慢但漏電流較低、功耗較小。

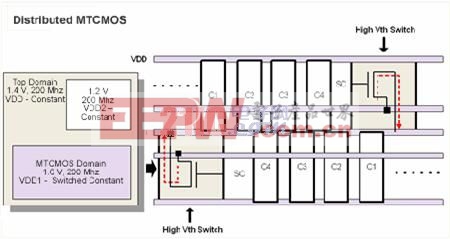

還有一種方式是利用高閾值電壓(high-Vt)開關來有選擇地切斷設計中未工作部分的電源。利用高閾值電壓開關來連接全局恒定電源線軌與局部開關電源線軌,讓局部線軌的電源根據需要開啟或關閉,這就提供了對功率門控的細粒度、中粒度和粗粒度的控制能力(如圖3)。

圖3. 多閾值CMOS晶體管能被用于功率門控,通過提供對局部電源導軌的細粒度控制從而降低功耗。

不過,所有這些方式都必須與功率分布網絡設計工作同步進行,而不是在設計流程后期單獨進行。首先,早期線軌分析必須在電源網格還未完成時執行,這樣耗能元件才可均勻地分布在芯片中,避免熱點和局部電壓降問題。其次,要有選擇地使用線寬算法來解決電壓降和電遷移問題。當然,這些技術都要求有早期集成化分析。

評論