電鍍用脈沖電源的研制

4.1設計思路

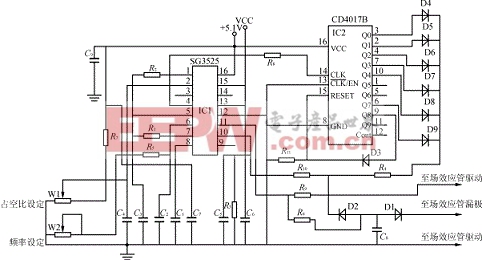

以SG3525PWM芯片為核心進行控制系統的設計。通過用CD4017B芯片進行8分頻,對輸出最大占空比進行限制。主電路采用場效應管并聯。電壓斬波控制原理圖如圖2所示。

圖2電壓斬波控制原理圖

4.2主電路的選擇

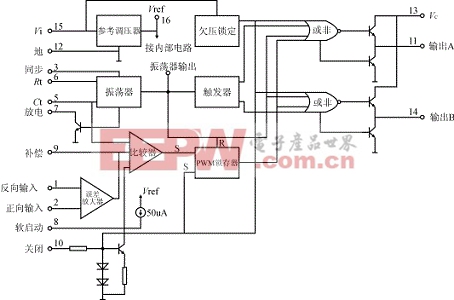

因為主電路為電壓斬波,存在著大電流的沖擊,為此,本裝置采用場效應管并聯。選IR公司的產品FB180SA10比較適合,它的VDSS=100V,RDS(ON)=0.0065Ω,ID=180A(TC=25℃)或120A(TC=120℃),同時,它用絕緣TO227封裝,易于并聯,內部電感量低。本裝置選用12只并聯。4.3控制與保護SG3525原理框圖如圖3所示。其具有5.1V溫度系數為1%的基準穩壓電源,誤差放大器,頻率為100Hz~400kHz(其值由外界電阻Rt,電容Ct決定)的鋸齒波振蕩器,軟啟動電路,同步電路,關閉電路,脈寬調制比較器,RS寄存器及保護電路。

圖3 SG3525原理圖.

利用SG3525的誤差放大器的1腳和2腳對輸出進行占空比的調節;在實際調試過程中發現,由于占空比較小,電壓比較器輸入電壓可以調節的范圍特別小,調試非常困難,為此特別設計了分頻線路即利用CD4017B十進制計數芯片及其外圍線路對SG3525的4腳振蕩器輸出信號進行8分頻,利用SG3525的10腳關機功能,封鎖SG3525的4腳輸出信號8個中的6個,使11和14腳各有1個脈沖輸出,見圖4、圖5。因為11腳最大占空比為48%左右,則分頻后實際輸出占空比最大為12%左右,最小占空比通過R7來確定。本部分的保護采取單周期限流保護,以場效應管的柵源電阻為采樣信號,當電流超過限定值時,通過SG3525的10腳將該周期驅動信號關斷,達到單周期保護。

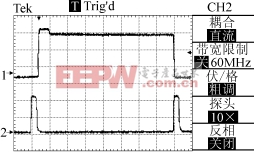

圖4 SG3525的4腳與11腳正常情況下的波形圖

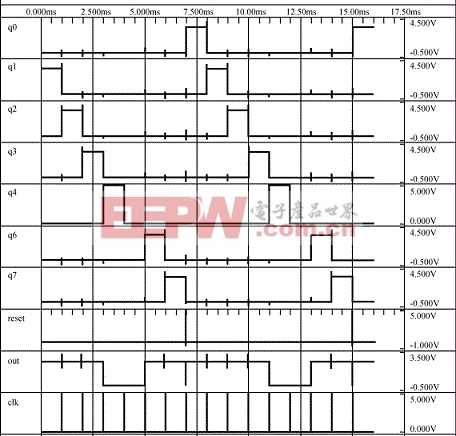

圖5 CD4017B及外圍線路輸入與輸出的仿真圖

4.4仿真與試驗

圖4給出了SG3525沒有分頻時,振蕩器輸出(4腳)CH1與PWM輸出(11腳)CH2的對應關系。由圖中可以清楚地看出振蕩器輸出脈沖出現在PWM脈寬的前后側各一個,其脈寬約在5μs~10μs,這個時間足夠CD4017B完成動作。圖5給出了CD4017B及外圍線路輸入輸出仿真圖。由圖5我們可以清楚看出CLK端輸入頻率1kHz脈寬為5μs的脈沖時,輸出OUT即D5~D9的陰極的波形與設計是相符的。經過濾波后,到達SG3525的10腳波形是比較規整的。為分析方便,同時給出了相關引腳的時序圖。同時,采取CLK上升沿翻轉,保證了控制時序的正確,采用封鎖6個脈沖,避免了干擾和初始狀態對輸出的PWM波形的影響。

5結語

該裝置投入運行后,經過將近一年的現場檢驗,證明運行穩定可靠,各項技術指標達到了設計要求,提高了電鍍產品質量,節省了電鍍時間,完全滿足該項工藝要求。

評論