一種改進的基于掃描的電路設計

2.2 多輸入特征寄存器(MISR)本文引用地址:http://www.j9360.com/article/179024.htm

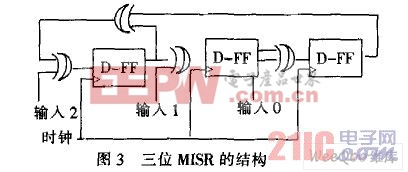

多輸入特征寄存器(Multiple Input Signature Reg—ister,MISR)是線性反饋移位寄存器的一種。如圖3所示,將待測電路的輸出部分加入線性反饋移位寄存器里,就成為一個多輸入特征寄存器。

多輸入特征寄存器最主要的特性是它的狀態。即其寄存器的值,不僅與現在的狀態有關,還與當時的輸入值有關,可以表示為:Next state=MISR(Cur—renLstate,Input),而其中MISR(……)可以代表特征式不同的多輸入特征寄存器。

為了減少基于掃描的電路設計的測試時間,就必須深入了解它的電路設計,了解為何其會消耗那么多的測試時間,然后來改進測試架構。

3.1 用向量壓縮來減少測試時間

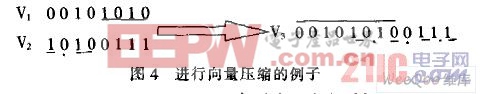

在測試過程中,我們有時可以發現,我們將要傳入掃描鏈的測試向量,已經部分地包含在已經傳入的測試向量序列中了,如圖4所示。V1向量的后半部分剛好等于V2向量的前半部分“1010”,如果在傳輸向量的時候,先傳輸V1再傳輸V2,那么我們就只需要將V2的后半段向量信息傳入掃描鏈就可以讓V2原本的信息在掃描鏈中完整地呈現,如圖中V3所示。很明顯,我們原來要輸入的測試向量的長度為16位,壓縮后只有12位,節省了V2的前半部分傳入掃描鏈的時間,從而減少了測試的時間,而且測試信息也沒有減少,不會影響故障覆蓋率。

3.2 用TEST—Per-Clock來縮短測試時間

我們對造成測試時間不夠理想的原因進行分析:

傳統的基于掃描的測試電路是采取TEST—Per—Scan的方式來進行測試的,也就是說要先將測試向量掃描到電路內的由掃描寄存器所組成的掃描鏈內。然后才可以完成一次測試;將測試向量掃描到待測電路這個步驟是一位一位地進行的,所以如果一個電路需要長度較大的測試的向量時,那么在這整個測試過程里。將會花很多的時間在將測試向量輸入到掃描鏈的這個步驟上,從而增加了測試時間。這個結構的測試向量的產生是利用LFSR產生出的偽隨機向量,并將其送入電路做測試。用LFSR產生測試向量會產生出許多沒有作用的測試向量,而這些沒有作用的測試向量又會產生大量多余的時間將其送入掃描鏈中,造成測試時間更嚴重的浪費。如果采用TEST—Per—Clock的方式做測試,在掃描鏈里原本的測試向量,在用一個時鐘的時間移進來一位之后,掃描鏈所含的值即是測試向量,對待測電路而言,其實都是一個新的測試向量,而且也具有偽隨機向量的特性,如果此測試向量是有效的,我們的測試時間就只用了一個時鐘的時間,而如果此測試向量無效,原本測試到沒有作用的測試向量時所需的付出的時間代價,由于用了新的測試向量填滿整個掃描鏈所需的時間,減少到只需一個時鐘移進一位的時間。

評論