基于PEMFC的控制系統電源的設計分析

實際取10匝。

對24 V輸出:

實際取42匝。

2.3 整流濾波

(1)輸出濾波電感的設計。輸出濾波電感中的電流除存在直流分量外,并且疊加一個較小的交流分量。輸出濾波電感的設計一般要求電感電流的最大脈動量為最大輸出電流的10%~20%。

對于輸出電壓Vo=5 V,輸出電流Iomax=1 A,最大占空比Dmax=0.63。

代入這些值則得:L=462.5μH。

對于輸出電壓Vo=24 V,重復上面的計算可得:L=0.004 4 H。

(2)輸出濾波電容的選擇。輸出濾波電容上的紋波電流:

根據上一節得到的數據,將ISRMS1=1.712 A,ISRMS2=0.856 A分別代入上式中,可求得Iri11.39 A,Iri2=0.695 A。濾波電容在20 kHz時的紋波電流應大于等于Iri。

輸出的紋波電壓由式Vri=IsprO決定。濾波電容C2,C3,C4選用330μF/50 V,C5選用100 μF/25 V。

3 控制電路的設計

3.1 PWM控制電路

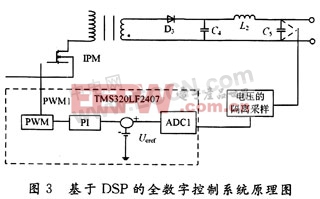

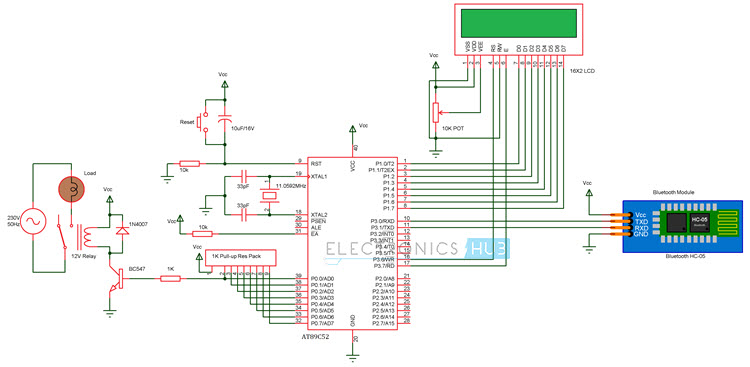

這里以數字信號處理器(DSP)TMS320LF2407為核心,設計了全數字PWM控制系統,如圖3所示,具有更好的實時性,能很好的適應PEMFC發電機的輸出特性。

輸出電壓經霍爾電壓傳感器隔離采樣后送到DSP的ADC模塊進行模數轉換,這些值在一定時間內經過一系列數字PI控制后,給全比較單元產生一個新的比較值,該比較值將在下一個開關周期改變PWM波形的占空比,這樣就達到了控制輸出電壓為所要求值的目的。

DSP中并沒有自動生成PWM信號的功能,要通過編程的方法實現它,通過一個單比較1的輸出腳PWM1實現所需要的PWM信號,下面具體介紹這種方法。單比較單元有一個比較寄存器,用來存儲比較值,當計數器于比較值相等時,相應的PWM輸出引腳電平發生跳變,怎樣跳變取決于PWM引腳的工作方式。

PWM輸出腳工作方式:有效高方式,有效低方式等。在定時器1工作在連續增減計數時,電平的為:輸出腳若設置為有效高,計數器為零時,輸出腳電平為零,計數器開始增計數,當與比較值相等時,這時輸出腳為有效狀態,電平變高。計數器到達周期值后,開始減計數,當減計數到比較值時,輸出腳為無效狀態,電平變低。輸出腳若設置為有效低。則此時的電平變化與有效高狀態正好相反。本文采用有效高工作方式。

T1CNT為計數器1的計數值,T1PER為計數器l的周期值。當T1CNT的值增加到與T1PER相等時,計數器1開始減計數,當T1CNT的值減到0時,計數器增計數。計數器值隨時間變化如圖4所示。在計數器的計數值與各比較單元的比較寄存器值(SCMPRl)相等時,輸出腳電平發生變化。波形圖如圖4所示,從圖中可以看出,計數器值通過與實時變化的比較寄存器值(SCMPR1)相比較,可以調節PWM脈沖寬度,進而改變功率管的占空比,達到對DC/DC變換器輸出電壓的實時控制。

評論