一種基于第二代電流傳輸器的積分器設計

電源電壓為±1.65 V,當在Y端輸入為高電平時,n型差分對M1和M2工作,由于MOS管的柵極不汲取電流,則有iY=0。設在Y端有小信號輸入,產生的漏極電流通過電流鏡M6和M5鏡像到M2,即有,iD1=iD5,iD5=iD6,可得iD6=iD2=iD1。設圖中M1、M2、M5、M6均工作在飽和狀態,兩個差分對的器件參數完全對稱,由晶體管飽和區的漏極電流

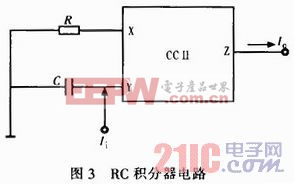

1.3 電流積分器結構

由CCII和RC構成的電流積分器如圖3所示。本文引用地址:http://www.j9360.com/article/176407.htm

假設電容C初始電壓為零,根據CCII端口特性得到:

在對數坐標下,電流增益與輸入信號頻率成線性關系。

2 電路仿真

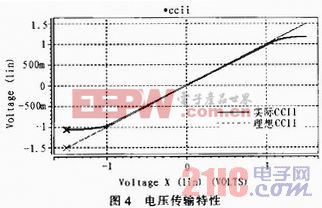

為了驗證電路的性質,對上述電路進行Hspice模擬仿真。仿真參數采用0.18μm CMOS工藝參數。

2.1 CCH電路仿真

圖2中各MOS管的尺寸如表1所示。圖中電源電壓VDD=1.65 V,VSS=-1.65 V。

圖4和圖5分別為CCII的電壓跟隨和電流跟隨特性。由圖可見,電壓跟隨的線性范圍為-1.04~1.15 V,電流跟隨的線性范圍為-9.02~6.66 mA。

基爾霍夫電流相關文章:基爾霍夫電流定律

評論