基于高速超微型C8051F300單片機的CCD驅動電路設計

CCD廠家眾多,型號各異,其驅動時序的產生方法也多種多樣,一般有以下4種:

(1)數字電路驅動方法

這種方法是利用數字門電路及時序電路直接構建驅動時序電路,其核心是一個時鐘發生器和幾路時鐘分頻器,各分頻器對同一時鐘進行分頻以產生所需的各路脈沖。該方法的特點是可以獲得穩定的高速驅動脈沖,但邏輯設計和調試比較復雜,所用集成芯片較多,無法在線調整驅動頻率。

(2)EPROM驅動方法

這種驅動電路一般在EPROM中事先存放所有的CCD時序信號數據,并由計數電路產生EPROM的地址使之輸出相應的驅動時序。該方法結構相對簡單、運行可靠,但仍需地址產生硬件電路,所需EPR0M容量較大,同樣也無法在

線調整驅動頻率。

(3)微處理器驅動方法

這種方法利用單片機或DSP通過程序直接在I/O口上輸出所需的各路驅動脈沖,硬件簡單、調試方便、可在線調整驅動頻率。但由于是依靠程序來產生時序,如果程序設計不合理,會造成時序不均勻;而且往往會造成微處理器資源浪費;通常驅動頻率不高,除非采用高速微處理器。

(4)可編程邏輯器件驅動方法

這種設計方法就是利用CPLD、FPGA等可編程邏輯器件來產生時序驅動信號,硬件簡單、調試方便、可靠性好,而且可以得到較高的驅動頻率。同樣也可在線調整驅動頻率。電路設計完成以后,如果想更改驅動時序,只需將器件內部邏輯重新編程即可。

以上4類方法中目前常用的是微處理器驅動方法(通常又稱為“軟件驅動”法)和可編程邏輯器件驅動方法(又稱“硬件驅動”法)。由于在CCD應用系統中,一般都要用到微處理器,所以若采用“軟件驅動”法,則無需增加硬件,在電路結構上最為簡單,系統成本也最低,因此,只要能克服其驅動頻率低、資源浪費多、時序不均勻等缺點,無疑是一種理想的驅動方法。本文結合Toshiba公司的TCDl206線陣CCD,介紹如何利用C8051F300來產生其要求的驅動時序。

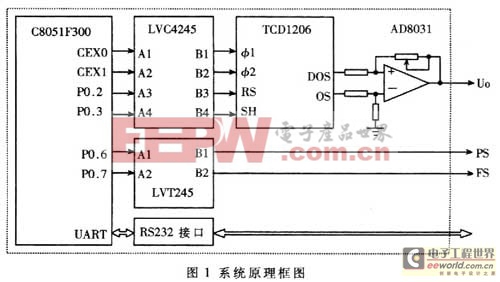

2 硬件設計

如圖1所示,虛線框內的電路構成CCD驅動處理板。安裝在CCD相機內部。系統處理器采用美國Silabs公司推出的超微型高速8位單片機C8051F300,CCD采用Toshiba公司的高靈敏度線陣CCD圖像傳感器芯片TCDl206,雙電壓供電的總線驅動器LVC4245解決了單片機(3.3V)和CCD(5V)二者之間的電平匹配。CCD驅動脈沖由C8051F300提供,其像素輸出電壓經高速運放AD8031處理,由U0引腳引到外部,同時向外部提供像素同步信號PS和行同步信號FS(由PO.6、P0.7經LVT245總線驅動器所得)。

U0、PS、FS這3個信號供外部處理器采集CCD像元輸出。另外,有時可能要在線調整CCD的某些參數(如驅動頻率、積分時間等),為此設置了RS232串口與外部處理器進行通信。

2.1 TCD1206

TCD1206是Toshiba公司生產的高靈敏度二相雙溝道線陣CCD圖像傳感器芯片,2160個有效像素點,像素頻率為0_3~2MHz(本系統為1.MHz),其驅動時序波形如圖2所示。

圖2中:φl、φ2為像素脈沖,兩者互為反相,RS為復位脈沖.SH為光積分脈沖,OS為像元輸出,DOS為像元補償輸出。當SH為低電平時,在φ1、φ2交變后,OS輸出像元電壓信號,隨后發RS脈沖,以便去掉信號輸出緩沖中的殘余電荷,為下一點像素電壓輸出做準備。各脈沖具體時序關系可參見參考文獻。

2.2 C8051F300

C8051F系列單片機其CPU內核采用流水線結構,機器周期由標準8051的12個系統時鐘周期降為1個系統時鐘周期,使其執行速度在相同晶振下是標準8051的12倍,處理能力大大提高,大部分C8051F單片機的峰值處理速度是25M1PS,而C8051F12X、13X系列的峰值處理速度則達到了100MIPS。C8051F系列單片機功能齊全,性能優異,其整體性能超過很多目前的16位單片機,甚至在一些低端應用中可取代低速的16位DSP器件,目前在儀器儀表、工業控制、嵌入式產品等領域日益得到廣泛應用。

C8051F300是C8051F系列中的超微型高速混合系統級單片機,是目前世界上最小封裝的8位單片機,11個引腳,封裝在面積為3ram×3mm的芯片上。內部集成了3個16位定時器、3個可編程捕捉,比較模塊、1個UART串口、1個I2C串口、1個8通道500KSPS采樣率的8位ADC、8KB的Flash程序存儲器、256B的內部RAM、8個I/O口,系統內部振蕩時鐘為24.5MHz(±2%)、最大峰值處理速度可達25MIPS。

由圖2可見,在4路CCD驅動脈沖中,對時序要求嚴格的是φ1、φ2和RS,為此,利用C8051F300的可編程計數器陣列模塊的2個可編程捕捉,比較模塊輸出口(CEXO、CEXl)自動產生φl、φ2,以CEXO為基準點,再產生RS和其他脈沖。

2.3 可編程計數器陣列(PCA)

PCA提供增強的定時器功能,由一個專用的16位計數器,定時器和3個16位捕捉,比較模塊組成,每個捕捉/比較模塊有其自己的I/O口(CEXn,n=l,2,3)。計數器,定時器的時基信號可在6個時鐘源中選擇:系統時鐘、系統時鐘/4、系統時鐘/12、外部振蕩器時鐘/8、定時器0溢出或ECI輸入引腳上的外部時鐘信號。而每個捕捉,比較模塊都可以被獨立配置為6種工作方式之一:邊沿觸發捕捉、軟件定時器、高速輸出、頻率輸出、8位PWM和16位PWM。

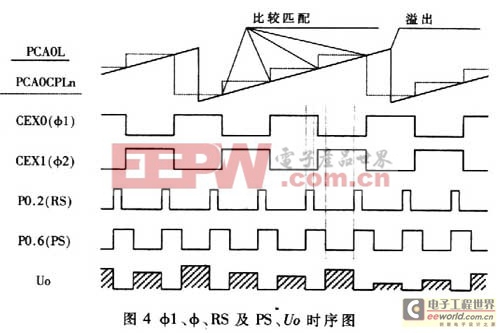

由于φ1、φ2(對應CEXO、CEXl)是占空比為50%的方波,所以捕捉/比較模塊0、1工作在頻率輸出方式,這種工作方式可在CEXn引腳產生可編程頻率的方波,其工作原理圖如圖3所示。當PCA計數器低字節與捕捉,比較寄存器低字節相同即PCAOL=PCAOCPLn時,稱為“比較匹配”,此時CEXn引腳電平翻轉,同時捕捉/比較寄存器高字節即PCAOL與PCAOCPHn相加后的結果送入PCAOCPLn,以便下一次比較用。顯然,只要改變PCAOCPHn的值,便可在CEXn引腳上得到頻率可調、占空比為50%的方渡,其頻率由下式定義:

fCEXn=fPCA/(2×PCAOCPHn),

其中:fPCA是PCA計數器,定時器的時鐘頻率。

3 軟件設計

為了得到時序嚴格的ccD驅動脈沖和外部輸出同步脈沖,程序不是靠軟件延時來達到合適寬度的脈沖,而是利用PCA模塊本身強大的功能,用中斷程序來完成各路脈沖,即開放捕捉,比較模塊0的“比較匹配”中斷作為同步信號,并以此為基準點完成相應脈沖的每一次變化。

3.1 CCD驅動脈沖

PCA的2個捕捉,比較模塊工作方式設置為如圖4所示的頻率輸出方式。其輸出引腳CEX0、CEXl的初始電平設置為1、0,當PCAOL與PCAOCPLn(n=O、1)“比較匹配”時,電平翻轉,由此形成反相的φ1、φ2脈沖;而HS脈沖的產生,則是在捕捉/比較模塊O的“比較匹配”中斷程序中,即先對RS(P0.2)置l,隨后清零,這樣就可產生80ns的RS脈沖(SETB bit指令周期為2個時鐘周期,即80ns)。

3.2 外部輸出同步脈沖及像素電壓

行同步信號FS、像素同步信號IX5均設置為低電平有效,CCD時序中φl、φ2交變后直到像素電壓輸出有一個延遲時間tdly(典型值為150ns),但由于捕捉/比較模塊0“比較匹配”時,一方面CEXO(φ1)翻轉,一方面向CPU請求中斷,而中斷響應時間需5個時鐘周期(200ns),顯然大于tdly,所以進入中斷后,不必考慮tdly,可直接對PS(P0.6)清零,待合適的時間后再將PS置1.這樣就產生一個低電平有效的PS信號。

CCD像素輸出OS、DOS經高速運放AD8031處理后,其外部輸出像素電壓Uo時序如圖4所示。

針對單片機在CCD時序驅動應用中存在的優缺點.選用新型高速C8051F單片機,實現CCD驅動電路,克服了單片機驅動方式存在的驅動頻率低、系統資源浪費、時序間隔不均勻等缺點;具有硬件結構簡單、調試編程方便、可在線調整驅動頻率等優點。本文所介紹的驅動電路己應用于TCDl206,超微型的封裝結構使其很容易與其他芯片一起嵌入在CCD相機中,系統運行可靠。

評論