I2C總線的單片機C語言實現及其應用

I2C(Intel-Integrated Circuit)總線是荷蘭的Philips公司于八十年代初推出的一種芯片間串行總線擴展技術。它用兩根線(數據線SDA、時鐘線SCL)可完成總線上主機與器件的全雙工同步數據傳送,可極方便地構成多主機系統和外圍器件擴展系統。I2C總線支持所有NMOS、CMOS、TTL等工藝制造的器件,其上所有的節點都連到同名的SDA、SCL上。I2C總方法,數據傳送都有相同的操作模式,接口電器特性相同且獨立,可在系統供電情況下從系統中移去或增加IC芯片,有I2C接口的外圍器件都有應答能力,讀寫片內單元時有地址自動加1功能,易實現多個字節的自動操作。近年來,國際上有關公司制造了多達幾百種的I2C總線器件,如8051系列單片機8XC752、LCD驅動器、RAM、I/O接口等芯片都使用了I2C總線接口。隨著數字技術的發展,I2C總線控制系統已經應用于越來越多的電子產品。

2 I2C總線的數據傳輸

2.1 接口特性

I2C總線接口的數據線SDA和時鐘線SCL必須經過上拉電阻接到正電源VDD上,各個I2C接口電路輸出端必須是漏極開路或集電極開路,以便完成“線與”的功能。I2C的SDA和SCL都是雙向傳輸線,當總線空閑時,此兩線都是“1”(高電平)。由于不同的器件都會接到I2C總線,邏輯的“0”(低)及“1”(高)的信號電平取決于VDD的電壓。總線上能連接的最大器件數取決于其電容容限400PF。

2.2 I2C總線上的傳輸時序

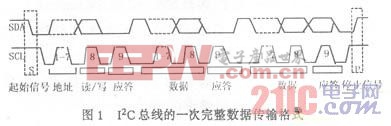

I2C總線上每傳輸一位數據都有一個時鐘脈沖相對應,在標準模式下可達100 kbit/s,高速模式下可達400kbit/s,總線上依據器件功能不同可建立簡單的主/從關系(master/slave),只有帶CPU的器件才可成主控器。圖1為I2C總線一次完整的數據傳輸。SCL為高期間,SDA狀態必須穩定,SCL為低時才允許SDA狀態變化。SCL保持高電平期間,SDA出現由高至低的轉換將啟動I2C總線,出現由低至高的轉換將停止數據傳輸。起始和終止信號通常由主控器產生。I2C總線的信號時序有嚴格規定,本應用采用標準模式,SCL低電平周期≥4.7μs,SCL高電平周期≥4.0μs,START和STOP之間的總線空閑時間≥4.7μs。

I2C 總線上傳送的每個字節必須為8位,啟動和停止之間可傳輸的數據字節數不受限制。采用串行傳送,首先傳送最高位,每傳送一個字節后必須跟一個應答位。主控器產生應答所需的時鐘脈沖期間,發送器必須釋放數據線(SDA為高),以便接收器輸出應答位。低電平為應答信號,高電平為非應答信號。非應答信號是當主控器作為接收器時,收到最后一個字節數據后,必須發送一個非應答信號給被控發送器,使被控發送器釋放數據線,以便主控器發停止信號,終止數據傳送。當從器件不能再接收字節時也會出現非應答信號這種情況。

I2C總線上的器件一般有兩個地址:受控地址和通用廣播訪問地址,每個器件有唯一的受控地址用于定點通信,而相同的通用廣播訪問地址則用于主控方同時對所有器件進行訪問。如圖1所示,起始信號后主控器發送的第一個字節就是被讀器件的受控地址,稱作尋址字節。尋址字節由高7位地址和最低1位方向位組成,方向位為“0”表明主控器對被控器的寫操作(W),方向位為 “1”表明對被控器的讀操作(R)。總線上每個器件在起始信號后都把自己的地址與尋址字節的前7位相比較,如相同則器件被選中,產生應答,并根據讀寫位決定在數據傳送中是接收還是發送。無論是主發、主收還是從發、從收,都是由主器件控制,數據傳送完后,主控器都必須發停止信號。

C51語言是針對Intel的8位單片機MCS-51系列而開發的、具有一般C語言特點的高級編程語言。從1985年至今,有許多公司推出 51系列的C語言編譯器,其中以Franklin C51編譯器在代碼生成方面較為領先,它可生成最少的代碼,支持浮點和長整數、重入和遞歸。頭文件reg51.h中包含了51單片機的特殊功能寄存器(SFR)的字節定義與位定義。為了與具有I2C總線接口的51單片機兼容,可在程序開始處定義單片機的P1.6和P1.7作為I2C總線的SCL和SDA信號,實際中也可用其它的I/O引腳作為SCL和SDA信號。C51語言中只要用賦值語句”=”就可實現I/O口某位的數據輸出和讀入。現將I2C總線底層讀寫函數接口及功能列舉如下,它可用于沒有內部I2C接口的51系列單片機與I2C總線器件通信。

#include<reg51.h>

/*全局符號定義*/

#define HIGH1

#define LOW 0

#define FALSE0

#define TRUE1

#define time 1

#define uchar unsigned char

#define uint unsigned int

sbit SCL=P1^6;

sbie SDA=P1^7;

1)函數原型:void delay(uchar nu m)

功 能:用for()循環提供延時。在實際應用中可依具體情況改變傳入參數,但必須滿足I2C總線時序中對SCL高、低電平周期的要求,本應用中取1,調用形式為delay(time)。

2)函數原型:void start(void)

功 能:提供I2C總線工作時序中的起始位,在SCL=HIGH期間,SDA出現由高到底的轉變,返回前將SCL拉低,允許數據變化,準備傳輸。其中調用函數1。

3)函數原型:void stop(void)

功 能:函數提供I2C總線工作時序中的起始位,在SCL=HIGH期間,SDA出現由低到高的轉變。其中調用函數1。

4)函數原型:void sendbyte(uchar b,uchar*error)

功 能:在時鐘作用下,將入口參數b中8位數據由高至低通過SDA線發送,并讀回應答信號,存于指針變量*error中。其中調用函數1、2、3。

5)函數原型:void readbyte(uchar*b,bit Ack)

功 能:函數在時鐘作用下接收8位數據,存于*b中,先接收的為高位,并發送應答信號(Ack=0),當接收到最后一字節時發送非應答(Ack=1)。其中調用函數1、2、3。

6)函數原型:void send-n-byte(uchar*info,uint n,uchar address,uchar*fault) 功 能:向I2C器件連續發送n個數據字節,數據存于數組info[]中,address為器件受控地址,末位為0(寫),n個數據的地址可作為數據字節發送,或設置地址自動加減功能。*fault存收到的應答位。其中調用函數1-4.

7)函數原型:void receive_n_byte(uchar*info,uint n,uchar address,uchar*fault)

功 能:從I2 C器件連續接收n個字節的數據,存于數組info[]中,address為器件地址,本函數保證器件地址末位是1(讀),n個數據的器件內地址可作為數據字節發送,或設置地址自動加減功能。收最后一字節時發非應答信號1。*fault存收到的應答位。其中調用函數1-5。

以下僅以sendbyte()函數原型為例說明C51如何具體實現I2C總線的發送:

void sendbyte(uchar b,uchar*error)

{int count;

bit data_bit;

*error=0;

for(count=7;count>=0;count--)

{data_bit=(bit)(b&0x80);

b=b<<1;

/*送數據位,產生時鐘脈沖*/

SDA=data_bit;

SCL=LOW;delay(time);

SCL=HIGH;delay(time);

SCL=LOW;delay(time);

}

/*釋放數據線,產生時鐘脈沖,讀回應答*/

SDA=HIGH;

SCL=LOW;delay(time);

SCL=HIGH;delay(time);

*error=(uchar)SDA;

/*釋放數據線,時鐘置低*/

SDA=HIGH;

SCL=LOW;delay(time);}

評論