利用單片機和CPLD實現直接數字頻率合成(DDS)

直接數字頻率合成(DDS)技術是美國學者J.Tierncy,C.M.Rader和B.Gold在1971年首次提出的。這是一種全數字技術,該技術從相位概念出發直接合成所需要的波形。同傳統的頻率合成技術相比,DDS技術具有很多優點:頻率切換時間短、頻率分辨率高、相位變化連續、容易實現對輸出信號的多種調制等[5]。但是由于當時的技術以及器件水平的限制,它的性能指標還無法與已有的技術相比,因此該技術當時并沒有引起足夠的重視。最近幾年來,隨著技術和器件水平的提高,國外一些公司先后推出各種各樣的DDS專用芯片,如 Qualcomm公司的Q2230、Q2334, AD公司的AD9955、AD9850等[3]。這些產品的問世,為電路設計者提供了良機,滿足了工程實際的需要。然而,商用DDS專用電路芯片也有它的的局限性,并不能滿足所有要求。例如,在實現線性調頻(LFM)等復雜的調制功能時,利用現有的商用芯片就會遇到一些困難[8]。由于近幾年來可編程器件CPLD 、現場可編程門陣列FPGA技術的迅速發展和廣泛應用,使用可編程器件實現DDS技術也越來越受到人們的關注。

本文引用地址:http://www.j9360.com/article/172132.htm1 DDS工作原理

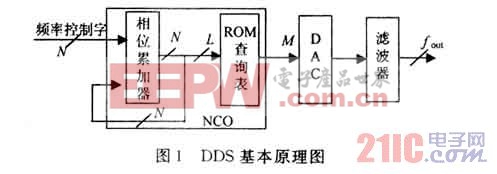

DDS工作原理框圖如圖1所示,其實質是以參考頻率源(系統時鐘)對相位進行等可控間隔的采樣。由圖1可見,DDS包括由相位累加器和ROM查詢表構成的數控振蕩源(NCO)、DAC以及低通濾波器(LPF)3部分。在每一個時鐘周期,N位相位累加器與其反饋值進行累加,其結果的高M位作為ROM查詢表的地址,然后從ROM中讀出相應的幅度值送到DAC。低通濾波器LPF用于濾除DAC輸出中的高次諧波。因此通過改變頻率控制字K就可以改變輸出頻率fout。容易得到輸出頻率fout與頻率控制字K的關系為:fout=Kfc/2N,其中fc為相位累加器的時鐘頻率,N為相位累加器的位數。定義當K=1為系統頻率分辨率,即。

2 系統的總體設計

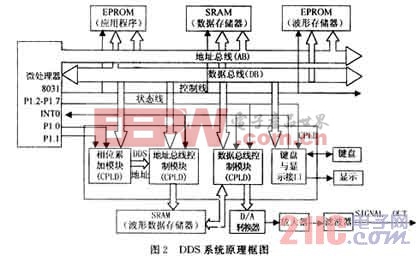

系統的原理框圖如圖2所示,本系統主要由單片機部分、DDS主通道部分、鍵盤及顯示部分以及輸出信號調理等部分組成。

單片機芯片采用的是比較常見的AT80C31芯片。同時片外還各擴展了1片程序存儲器2764與數據存儲器6264,分別用來存放運行中所需的程序與隨機數據。

DDS主通道部分是我們設計的關鍵所在,該部分主要由相位累加模塊、地址總線控制模塊、數據總線控制模塊與波形數據存儲器EPROM、SRAM等組成。其中相位累加模塊、地址總線控制模塊和數據總線控制模塊都是在CPLD上實現,采用的芯片是ALTERA公司的FLEX10K系列器件。我們將所需要合成的波形采樣數據固化在EPROM 2764中,但是我們知道EPROM的讀周期比較長,很難滿足系統的訪問時間要求。因此設計中又使用了1片HSRAM,在DDS系統合成波形的過程中,代替ROM進行波形數據的快速查詢。

鍵盤和顯示部分是系統和用戶進行交互的重要手段。這一部分的邏輯功能,也是在CPLD上實現的。

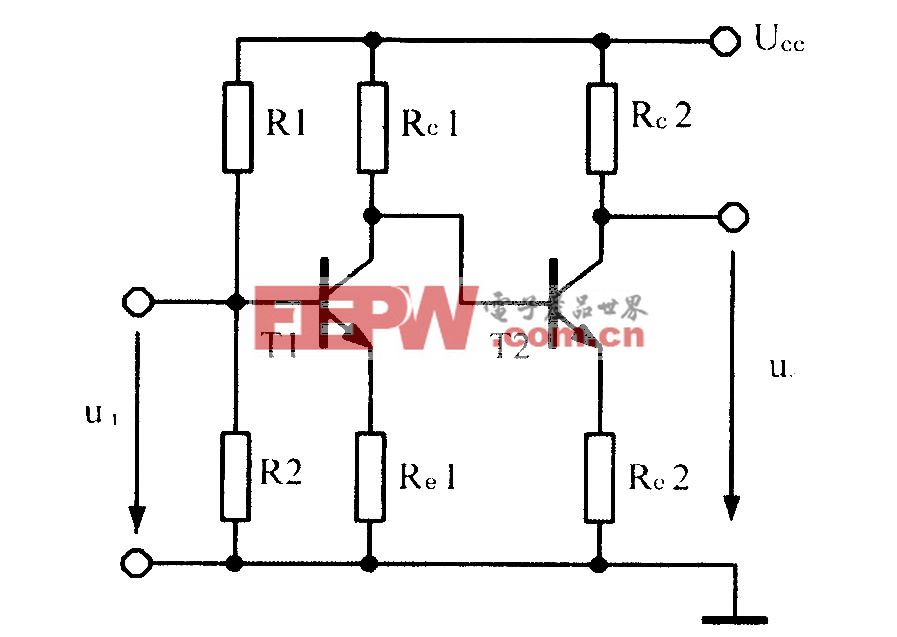

輸出信號調理部分是把從HSRAM中讀出的波形的數字幅度值首先轉換成模擬信號,然后再進行放大、濾波處理后輸出。這一部份包括D/A轉換器、幅度放大器和濾波器。DAC器件采用AD公司的12位AD9713B,該器件特點是具有較高的更新速率(100 MSPS)和較低的功耗(725 mW)[1],因此特別適合于DDS信號合成。幅度調節電路使用的是雙極性放大器AD708、AD9617和AD9713所組成的電路。

3 系統總體工作狀態說明

前面已經提到過,由于EPROM的讀取時間比較長,很難滿足系統對時間的要求,因此在系統中又增加了1片高速SRAM,作為波形數據緩存器。這樣,系統就有兩個工作狀態:首先,系統開始工作時,需要將波形數據從EPROM調到HSRAM中,即波形數據的加載狀態;數據加載完畢后,按照DDS合成原理進行信號合成,即信號的合成狀態。系統設計中使用單片機的P1口控制這兩種工作狀態之間的切換。

3.1 波形數據的加載

單片機系統上電自檢完畢后,開始進行波形數據加載過程。此時,地址總線控制模塊和數據總線控制模塊,將總線的控制權交給單片機系統。在該過程中,EPROM處于讀狀態,而SRAM為寫狀態。8031 按照EPROM、SRAM的時序要求,將8 k的波形數據從EPROM加載到HSRAM中。該過程大概需要幾毫秒時間。

由此我們知道,用這種方法不僅能夠合成標準波形(如:正弦波、方波、三角波等),而且還可以合成各種非標準波形。對此我們只要通過數據采集器或PC機獲得8 K的波形數據,然后存入到EPROM中,就可以按所需要的頻率輸出相應波形。

3.2 波形合成電路的設計

當波形數據加載完畢后,系統就可以進行信號合成。單片機將接收到的頻率值轉換成頻率控制字,送到相位累加器。相位累加器在每一個時鐘周期進行相位累加,然后將每次的累加和作為地址去尋址SRAM,讀出與該地址所對應的波形幅度值,然后送到D/A轉換器轉換成模擬信號,最后經幅度放大、濾波輸出。

評論