提高單片機設計硬件可靠性的一般方法

1、電路設計

本文引用地址:http://www.j9360.com/article/171713.htm影響單片機測控系統可靠性的因素,有45%來自系統設計。為了保證測控系統的可靠性,在對電路設計時,應進行最壞情況的設計。

各種電子元件的特性不可能是一個恒定值,總是在其標注值的上下有一個變化的范圍。同時,電源電壓也有一個波動范圍,最壞的設計(指工作環境最壞情況下)方法是考慮所有元件的公差,并取其最不利的數值。核算電路的每一個規定的特性。如果這一組參數值都能保證正常工作,那么在公差范圍內的其它所有元件值都能使電路可靠地工作。在設計應用系統電路時,還要根據元件的失效率特征及其使用場所采取相應措施:

在元件級,對那些容易產生短路的部件,以串聯方式復制;對那些容易產生斷路的部件,以并聯方式復制,并在這些部分設置報警和保護裝置。

2、元器件選擇

(1)型號與公差 在確定元件參數之后,還要確定元器件的型號,這主要取決于電路所允許的公差范圍。對于電容器,如果用于常溫環境中,一般的電解電容就可以滿足要求,對于電容公差要求較高的電路系統,則電解電容就不宜選用。

(2)降額使用 元件的失效率隨工作電壓成倍的增加。因此,系統供電電源的容量就大于負載的最大值,元器件的額定工作條件是多方面的,如電流電壓頻率、功率、機械強度以及環境溫度等。所說的降額使用,就是要降低以上這些參數,在電路設計中,首先考慮的是降低它的功效。選用電容器時要降低它的工作電壓,使用電壓一般小于額定電壓的60%。選用二級管以及可控硅時,應使其工作電流低于額定電流,對于晶體管、穩壓管等應考慮工作時的耗散功率。

集成電路的降額使用同樣是從電氣參數及環境因素上來考慮。在電氣上要降低功耗,對CMOS芯片和線性集成電路在滿足輸出要求的前提下,應降低電源電壓或減少下級負載。而TTL電路對電源電壓要求比較嚴,這時應注意它們的帶負載能力,民用元器件的溫度使用范圍較窄,如果用于工業控制中,在整體設計時應降額使用。

3、結構設計

結構可靠性設計是硬件可靠性設計的最后階段,結構設計時首先應注意元器件及設備的安裝方式;其次是控制系統工作的環境條件,如通風、除濕、防塵等。

4、噪聲抑制

噪聲對模擬電路會影響系統的精度,對數字電路會造成誤動作,因此在工程設計中,必須采用抑制措施。干擾信號可分為串模干擾和共模干擾兩大類。針對這兩類干擾成熟的電路以及專題著作也不少,下面將常用的方法介紹如下:

4.1 抗串模干擾的措施

(1)光電隔離,在輸入和輸出通道上采用光耦合器件來進行信息傳輸,以免上一級干擾竄到下一級。

(2)硬件濾波電路,常用RC低通道濾波器接在一些低頻信號傳送電路中(如熱電偶輸入線路等),它可大大削弱各類高頻干擾信號(如各類“毛刺”干擾)。

(3)過壓保護電路,在輸入輸出通道上應采用一定的過壓保護電路,以防止引入高電壓傷害單片機系統。

(4)采用抗干擾穩壓電源,微機系統的供電線路是干擾的主要入侵途徑。通常采用以下幾種措施:

①單片機系統的供電線路和產生干擾的用電設備分開供電;

②通過低通濾波器和隔離變壓器接入電網;

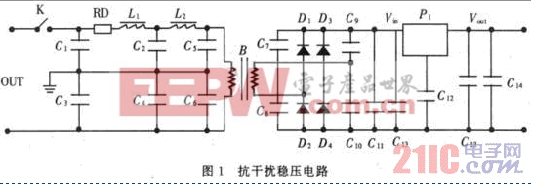

③整流元件上并接濾波電容,如圖1所示,選用高質量的穩壓電路。

4.2 抗共模干擾措施

共模干擾通常是針對平衡輸入信號而言的,抗共模干擾的方法有以下幾種:

(1)平衡對稱輸入,在設計信號源時,通常是各類信號盡可能做到平衡對稱。

(2)選用高質量的差動放大器。

(3)要有良好的接地系統。

(4)系統接地點要正確連接;系統中的大功率的元件地線與小功率的信號地線也要分開布線或加粗地線,數字地與模擬地必須分開,最后只在一點相連。如果系統中的數字地與模擬地不分,則數字信號電流在模擬系統的地線中形成干擾(地電位改變),使模擬信號失真,這一點請初學者特別注意。

(5)屏蔽,用金屬外殼或金屬匣將整機或部分元器件包圍起來,再將金屬外殼或金屬匣接地,就能起到屏蔽作用。對于各種通過電磁感應引起的干擾,特別注意的是屏蔽外殼的接地點,一定與信號的參考點相接。

以上介紹的幾項是十分必要的硬件抗干擾措施,它給單片機系統創造了一個基本上“干凈”的工作環境。

參考文獻

1 廣軍.實用接口技術.西安電子科技大學出版社,1997

2 毛楠,孫瑛.電子電路抗干擾實用技術.北京:國防工業出版社,1996

評論