低功率MCU設計--創新技術實現

嵌入式市場迫切要求以更低的功耗實現更高的性能,這一需求現已擴展到大量便攜式和墻上電源供電的應用中。為滿足該需求,飛思卡爾始終致力于將低功耗設計擴展到更廣的領域。最新推出的Kinetis(動力學)系列ARM Cortex-M4微控制器就是最新突破。2010年第四季度的數據抽樣表明,Kinetis代表著基于ARM Cortex-M4新內核的首款適合廣泛市場的混合信號MCU組合,同時也是業界擴展性能最強的ARM Cortex-M4 MCU的產品之一。多種硬件和軟件兼容的MCU產品系列將提供卓越的性能和內存容量,其擴展性強,從采用超小QFN封裝的50MHz、32KB閃存器件到帶1MB閃存和工業用豐富外設集的150MHz器件均包括在內。低功耗在Kinetis MCU設計中發揮著核心作用。這從采用了飛思卡爾最新90納米SG-TFS(分裂柵-薄膜存儲器)工藝技術,以及大量具有省電功能的通用、專用外設上都可以反映出來。

本文引用地址:http://www.j9360.com/article/171525.htm工藝技術是任何半導體產品的基本構建模塊和決定MCU功耗的關鍵因素。除了能夠提供超快訪問速度、防止充電損失外,Kinetis MCU還是首款利用了飛思卡爾SG-TFS閃存技術優勢的產品,該技術專門設計用來解決功耗敏感應用的需求。在設計SG-TFS位存儲單元時,飛思卡爾在讀取路徑上使用快速、低電壓的晶體管,從而將工作電壓降到1.71V至3.6V這一較低的范圍。在采用兩個1.5V電池的應用中,一旦電壓達到0.9V,電池壽命就會迅速縮短。這意味著與過去通常限制在2V甚至更高的MCU產品相比,1.71V的更低電壓限制可以大大延長電池壽命。擴展的電壓范圍不僅適用于片上存儲器:閃存、SRAM和飛思卡爾新的FlexMemory(可配置,耐用性強的EEPROM),同時也適用于模擬外設,因而即使在功率曲線的較低端也能實現連續的信號測量和調節。允許高速切換的信號工作在較低電壓(通常為1.2V)下,TFS的電壓特性還有助于降低運行電流。由于運行電流與C*V2*f成比例,電壓下降對有效電流的閃存組件非常有利。

必須具備的功率模式

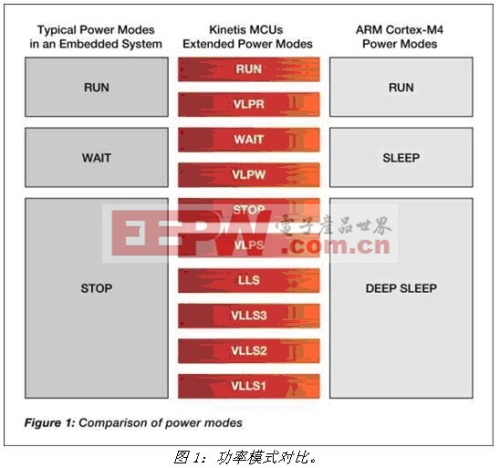

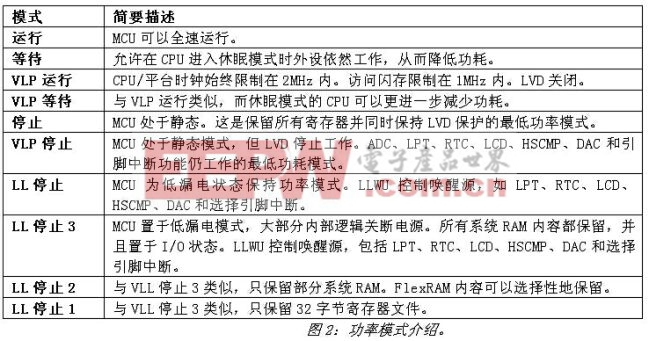

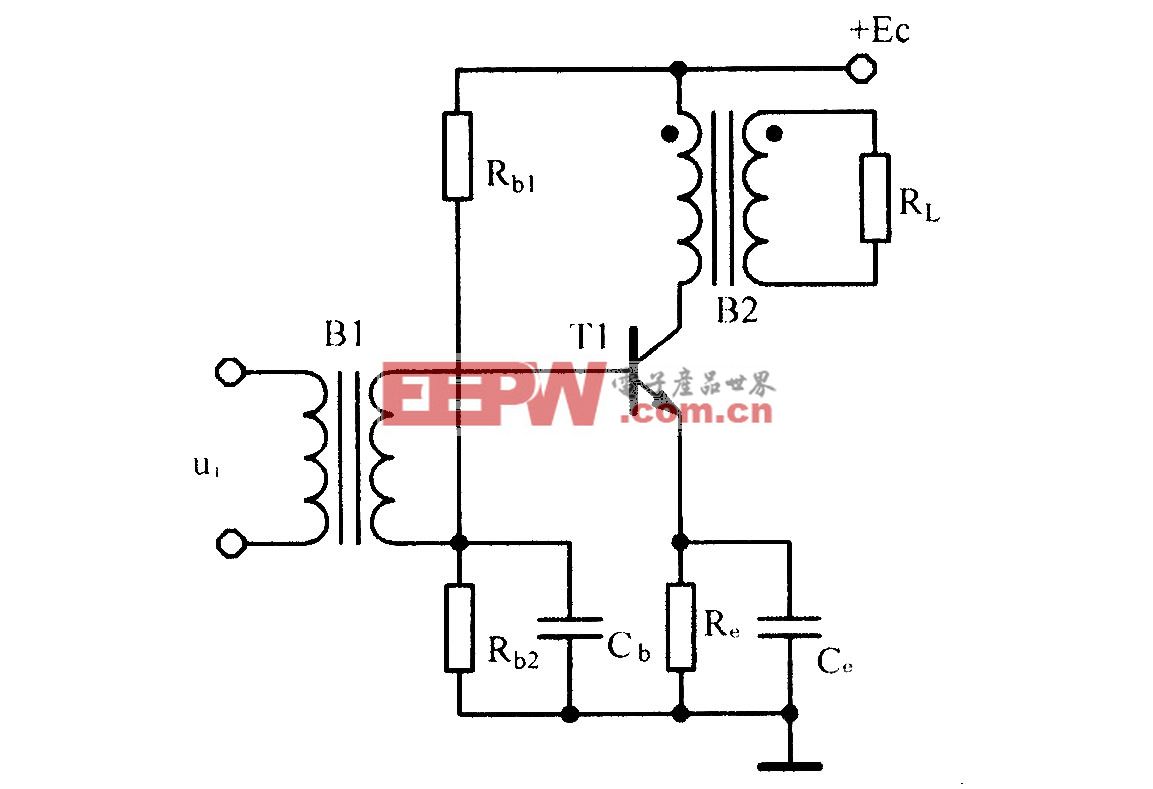

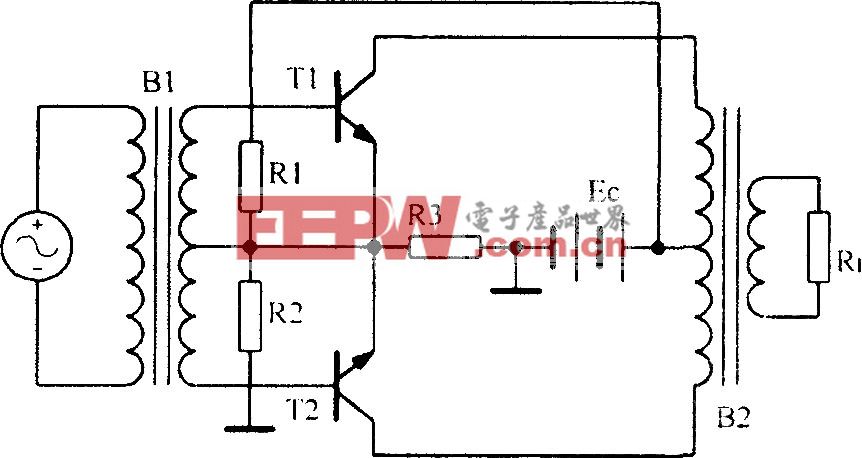

在電池供電的大部分應用中,CPU將大部分時間用于功率降低或休眠模式。因此,非常關鍵的一點是微控制器提供了極具吸引力的電源模式、喚醒源和啟動時間選擇,以便設計人員能夠優化外設活動和恢復時間來滿足應用需求,并最大限度地使用現有的可用能源。飛思卡爾的處理方式是在Kinetis MCU中配置不少于10種的運行、等待和停止模式,同時還配有多個喚醒源(見圖1和2)。每個運行模式都配有對應的等待和停止模式。飛思卡爾還推出了幾款低漏電模式和新的低漏電喚醒單元(LLWU),以滿足最嚴格的功率預算。

工作在運行模式下時,CPU全速執行代碼,可以實現低至200μA/MHz的功耗。對于不需要最大總線頻率的時段,可以使用極低功率運行(VLPR)模式。這就把CPU頻率限制在2MHz內,并將內部穩壓器置于待機模式,同時還保持外設和低電壓檢測(LVD)的全部功能實現。在這種模式下,使用600μA至1mA范圍的VLPR LDD可以節省大量功耗,具體情況則取決于MCU的性能、內存和外設配置。

評論