基于FPGA和51單片機信號發生器設計與實現

摘要:為了降低傳統函數信號發生器成本,改善函數信號發生器低頻穩定性,本文結合FPGA和51單片機設計并實現了產生以0.596Hz頻率精度各種函數信號。函數信號頻率、波形、幅度由51單片機控制,并用LCD顯示函數信號相關信息。本文設計的信號發生器易維護、可以軟件升級,從而得到更高頻率精度的函數信號滿足不同場合設計的需要。

關鍵詞:FPGA;51單片機;信號發生器;升級

信號發生器又稱為波形發生器是一種常用的信號源并且廣泛應用于電子電路、通信、控制和教學實驗等領域的重要儀器之一。為了降低傳統函數信號發生器成本,改善信號發生器低頻穩定性。筆者結合FPGA和51單片機產生0.596 Hz頻率精度函數信號。筆者設計通過51單片機控制函數信號類型以及相關參數,用戶可通過按鍵設置需要的波形、波形幅度、波形頻率以及方波的占空比、相位。本文設計方案不僅具有良好的經濟前景,也可以為當代高等教育深化改革做一個參考方向。

1 系統設計方案

1.1 系統硬件設計

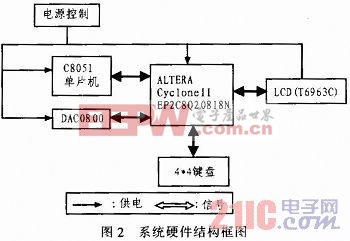

本文中設計中硬件包括EP2C8Q20818N芯片和C8051F0201單片機、DAC0800芯片,T6963的LCD。本文中主要利用FPGA(EP2C8Q20818N)橋接控制LCD、4×4鍵盤和DAC0800(C8051單片機和DAC0800有一條基準電壓信號),系統硬件設計框圖如圖2所示。本文中函數信號主要由FPGA(EP2C8Q20818N)產生;C8051單片機用作分析處理用戶信息、給DAC0800提供基準電壓以及控制FPGA(EP2C8Q20818N)產生需要用戶的函數信號。

1.1.1 EP2C8Q20818N簡介

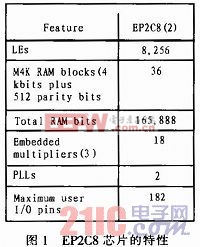

EP2C8Q20818N是ALTERA公司推出一款嵌入式FPGA(現場可編程門陣列)芯片。具有182管腳。下面列出它的特性表,如圖1所示。

評論