三階電荷泵鎖相環系統級設計與仿真驗證

摘 要: 本文采用鎖相環開環傳輸函數波特圖對三階電荷泵鎖相環進行了系統級設計,并且對相位裕度與建立時間,穩定性與環路帶寬這兩對矛盾進行了權衡。然后在SIMULINK中建立了包含電荷泵鎖相環離散時間特性和非線性本質的行為模型,并進行了仿真驗證。

關鍵詞: 電荷泵鎖相環; 時鐘合成器; 波特圖; 行為模型

引言

鎖相環是現代通信系統中的關鍵模塊,通常集成在系統芯片上,其主要應用領域為:數據通信中的時鐘與數據恢復、無線通信中的頻率合成器、微處理器中的時鐘合成與同步等。電荷泵鎖相環是當今最流行的鎖相環結構,為了減小壓控振蕩器控制電壓的紋波,它采用了二階無源環路濾波器,這樣就構成了三階電荷泵鎖相環。系統級設計與仿真驗證是鎖相環設計的第一步和關鍵的一步。本文對一種用作時鐘倍頻器的三階電荷泵鎖相環進行了系統級設計與仿真驗證,仿真環境采用SIMULINK。

圖1 電荷泵鎖相環結構

圖2 相位域模型

圖3 電荷泵鎖相環行為模型

電荷泵鎖相環的基本原理與設計方法

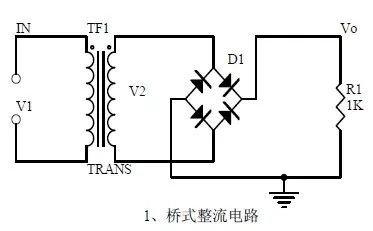

用作時鐘倍頻器的三階電荷泵鎖相環結構如圖1所示,包括由晶體振蕩器產生的參考時鐘、鑒頻鑒相器、電荷泵、環路濾波器、壓控振蕩器和分頻器。鑒頻鑒相器比較兩個信號的相位與頻率差,并產生控制信號給電荷泵,電荷泵相應地給環路濾波器充放電。壓控振蕩器的輸出頻率正比于環路濾波器上的控制電壓,最終使參考時鐘與分頻器的輸出信號同頻同相,即壓控振蕩器的輸出信號頻率為參考時鐘頻率的N倍。

一個電荷泵鎖相環的工作過程分為頻率牽引過程和相位鎖定過程,頻率牽引過程是一個完全的非線性過程,相位鎖定過程是一個近似的線性過程。電荷泵鎖相環本質上是一個離散時間采樣的動態系統,當環路帶寬遠遠小于參考時鐘頻率時,可以采用連續時間近似;當相位誤差在鑒頻鑒相器的鑒相范圍內時,可以采用線性近似。這樣,當電荷泵鎖相環處于相位鎖定過程時,就可以得到一個線性連續時間的相位域模型,如圖2所示。其中Kpfdcp是鑒頻鑒相器和電荷泵一起構成的鑒相器增益,并有Kpfdcp=Ip/2p,Ip為電荷泵的充放電電流,Kvco為壓控振蕩器的增益,N為分頻器的分頻比,F(s)為環路濾波器的傳輸函數。一階無源環路濾波器由一個電容C1與一個電阻R1串聯構成,二階無源環路濾波器中再加上一個電容C2與先前的R1C1并聯來減小控制電壓紋波,從而得:

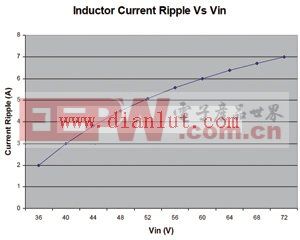

下面討論用開環傳輸函數的波特圖對三階電荷泵鎖相環進行系統級設計的方法,由圖2可以得到開環傳輸函數為:

令開環傳輸函數的單位增益帶寬為Wu,為了使開環傳輸函數在單位增益帶寬下的相位裕度最大,設G(s)的零點低于Wu,即Wz=Wu/X;同時設G(s)的極點以相同的比例因子高于Wu,即Wp=XWu,則開環傳輸函數被改寫為:

開環傳輸函數在單位增益帶寬的相位裕度為:

同時得開環傳輸函數單位增益帶寬為:

因此,可以把開環傳輸函數進一步改寫為:

從而得出三階電荷泵鎖相環的閉環傳輸函數為:

在本文設計的時鐘倍頻器中,晶振輸入的參考時鐘頻率為25MHz,壓控振蕩器的輸出增益為,電荷泵電流為100mA,分頻器的分頻比N=16。跟據前面的電路參數,電荷泵鎖相環的環路增益相對較高,為了保證電荷泵鎖相環的穩定性,并抑制控制電壓上的紋波,所以將此時鐘倍頻器中的三階電荷泵鎖相環設計成窄帶鎖相環,其開環單位增益帶寬為fu=Wu/2p=0.317MHz。同時,為了有相當的開環相位裕度和較快的閉環線性建立時間,取開環傳輸函數在單位增益帶寬的相位裕度,則有X=2.45。 最后得到C1=0.4167nF,C2=0.0833nF和R1=2.88KW。

圖4 輸入相位階躍時的波形

圖5 輸入頻率階躍時的波形

電荷泵鎖相環在SIMULINK中的建模與仿真

為了對所設計的三階電荷泵鎖相環進行系統級驗證并分析其動態特性,本文在通用的仿真環境SIMULINK中建立了其行為模型,并進行了動態特性的仿真驗證。

整個用作時鐘生成器的三階電荷泵鎖相環在SIMULINK中的行為模型如圖3所示,其中鑒頻鑒相器由兩個帶使能的D觸發器、一個與運算、一個非運算和一個延遲單元組成,兩個D觸發器的Q輸出端一方面作為控制信號up、down傳送給電荷泵,另一方面作為反饋信號產生與運算的復位信號;用一個脈沖發生器來代替參考時鐘,并與一個D觸發器的CLK端相連,另一個D觸發器的CLK端接分頻器的輸出信號。

電荷泵被模擬為一個減運算和一個增益級,增益級的增益為電荷泵的電流。二階無源環路濾波器被模擬為一個積分環節、一個增益級和一個傳輸函數環節,相應的參數由環路濾波器的傳輸函數F(s)確定。壓控振蕩器被模擬為一個增益級、一個相加運算、一個積分環節、一個模2p運算和一個開關環節,其中增益級的增益為壓控振蕩器的增益Kvco,相加運算的另一輸入端接的恒量是壓控振蕩器的中心頻率,積分環節將頻率變為相位,模2p運算把相位信號變為周期為2p的鋸齒波信號,開關環節再把周期為2p的鋸齒波信號變為方波時鐘信號。分頻器由四個異步二分頻器級連而成,每個異步二分頻器均是由!Q端與D端相連的D觸發器構成。

圖3所示的三階電荷泵鎖相環行為模型完全能夠模擬電荷泵鎖相環的離散采樣本質和非線性本質,這樣就可以通過仿真來得到比較接近實際情形的電荷泵鎖相環動態特性,并驗證采用線性連續時間近似理論所設計的電荷泵鎖相環。圖4是參考輸入信號發生相位階躍時環路濾波器輸出電壓的波形,此波形非常類似于將三階電荷泵鎖相環近似處理為線性連續時間系統時所得的瞬態響應,由圖4可以得到:建立時間tsettle=6ms。圖5是參考輸入信號發生5MHz頻率階躍時環路濾波器輸出電壓的波形,從起始時刻到波形第一次達到穩態值的時刻為頻率牽引過程,由圖可知頻率牽引過程是一個完全的非線性過程,時間為7.3ms;此后是相位鎖定過程,是一個近似的線性過程,時間為5.7ms。

結語

本文采用鎖相環開環傳輸函數波特圖對三階電荷泵鎖相環進行了系統級設計,并用SIMULINK進行了仿真驗證,對鎖相環設計中的相位裕度與建立時間,穩定性與環路帶寬這兩對矛盾進行了很好的權衡。

參考文獻

1 Behzad Razavi. Design of Analog CMOS Integrated Circuits.McGraw-Hill,2001

2 F. M. Gardner. Charge-pump phase-lock loops. IEEE Trans. Commun.,Nov.1980

3 Cicero S. Vaucher. An Adaptive PLL Tuning System Architecture Combining High Spectral Purity and Fast Settling Time. IEEE J.Solid-State Circuits,April 2000

評論