采用S3C44B0X的大型LED顯示系統設計

本文引用地址:http://www.j9360.com/article/167918.htm

1.2 主控電路與LED屏的接口設計

本顯示系統選用基于ARM7TDMI內核并帶有內部DMA控制器的S3C44BOX作主控制器,使其工作在ARM狀態,并使用16位總線。由于把LED屏虛擬的視為一段連續的存儲單元,故為其分配地址空間0x2000000~Ox4000000。

主控電路與LED屏接口應能實現以下功能:

◆選通任意位置的顯示模塊及該模塊上的第一級列數據鎖存器。將該位置要顯示的點陣碼準確鎖存,并能在第一級列數據鎖存器數據刷新后,將刷新數據鎖存到第二級列數據鎖存器并輸出。

◆能控制選通驅動16行同名行中的一行進行逐行掃描顯示。

◆實現主控芯片3.3 V到LED屏5V的邏輯電平轉換。

主控板與LED屏接口電路原理圖如圖2所示。

一個大型LED屏的結構可分為縱向級聯和橫向級聯,這種結構類似于一個三維數組。假設一個三維數組LED[i][j][k],其中:

i=0,1,2,…,m 表示LED屏縱向級聯級的序號。

j=0,1,2,…,n 表示LED屏橫向級聯級的序號。

k=O,1,2,…,16 表示顯示模塊上16個第一級列數據鎖存器的序號。

由于系統使用16位并行總線數據傳輸方式,并將LED屏視為一段連續的存儲單元,故使用A[4:1]作顯示模塊上選通第一級列數據鎖存器譯碼器(圖1中U2)的譯碼輸入,即為三維數組的k變量;使用A[8:5]作選通橫向級聯顯示模塊的譯碼器(圖2中U7)譯碼輸入,即為三維數組的j變量;由于LED屏要具有良好的靈活性,又由于采用DMA傳輸數據要求點陣碼存放順序的技術要求,縱向級聯級選通不滿足使用地址總線譯碼選通的條件,所以使用S3C44BOX的PG[2:0]作縱向級聯級選通譯碼器的譯碼輸入,即三維數組的i變量。

由于地址和數據總線上的狀態不斷變化,所以在對LED屏進行寫操作時,地址和數據信號應進行鎖存,主控板上分別使用U2、U3和U4鎖存對LED寫操作時的地址和數據總線的狀態。LED屏分配首址為Ox2000000,當對其進行寫操作時,S3C44BOX的nGCSl和nWE腳會出現可編程控制時延的有效低電平。nGCSl經一個非門作U2、U3和U4的鎖存使能控制信號,保證僅在對LED屏訪問時,地址和數據總線上的信號才被鎖存。nWE經一個非門作屏端第一級列數據鎖存器(圖1中U3~U19)的鎖存使能控制信號,保證只有當刷新數據穩定出現在列數據鎖存其輸入端時才被鎖存。S3C44BOX的PCI0作所有屏端第二級鎖存器(圖1中U20~U35)的鎖存使能控制信號線;S3C44BOX的PC[3:O]作16行驅動譯碼器(圖1中U1)的譯碼輸入。由于數據傳輸時只需要主控板對LED屏輸出控制,不需要信號反饋,所以接口電路采用廉價的5V供電的HCT電路芯片方案,就可滿足主控芯片3.3V到LED屏5V的邏輯電平轉換。

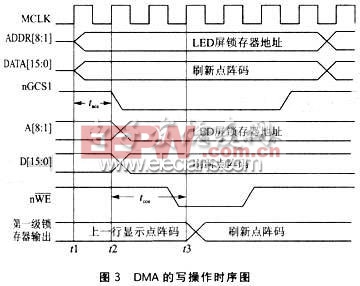

在DMA傳輸數據時,更關心的是DMA的寫操作,時序如圖3所示。t1時刻DMA寫操作開始,地址和數據總線上出現LED屏相應位置的地址和刷新數據;t2時刻nGCS1引腳出現有效低電平,地址和數據總線上的數據被鎖存到U2~U4并輸出;t3時刻nWE引腳出現有效低電平,U2~U4的輸出數據被鎖存到屏端第一級列數據鎖存器并輸出。這樣主控制器就完成了一次列數據的刷新。

評論