基于BF561的智能視頻監控儀的設計

傳統的監控系統需要安保人員實時監控畫面或事后回放視頻記錄進行人工分析,不但成本高,而且效率低。目前很多視頻監控系統也只是做到了網絡化,而且由于受網絡帶寬的限制,造成數據的延遲或丟失,也給監控系統帶來很大的風險。針對以上問題,本文設計并實現了一種基于BF561的智能視頻監控儀,可以與現有的監控系統實現無縫連接,實現目標的自動監控與跟蹤,有效地提高了監控效率。

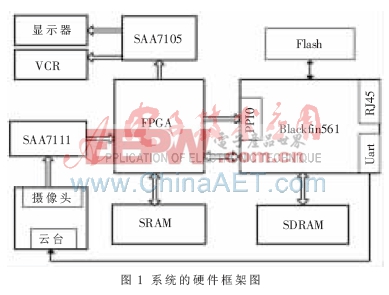

1系統硬件框架結構

由于在實時視頻處理系統中,底層算法的數據量大,運算結構相對比較簡單,對速度有很高的要求。而高層處理算法控制結構復雜,數據量較底層算法少,故本文采用FPGA+DSP的結構, 其系統的硬件框架如圖1所示。本設計采用ADI公司的嵌入式多媒體處理器BF561(BlackFin561)作為算法處理和控制核心,采用EP3C25F324C8對圖像進行預處理和圖像的背景提取等算法。BF561擁有2個600 MHz的DSP內核,每個內核提供兩套乘法器和ALU,有專門的視頻處理硬件單元和視頻處理指令,具有豐富的DMA通道和大容量高速的SRAM。BF561采用MSA結構,可作為RISC處理器使用,也可以作為DSP使用[1]。

1.1視頻采集和輸出模塊

本文采用解碼芯片SAA7111將攝像頭輸出的PAL制信號轉換為數字信號。SAA7111是飛利浦公司推出的9位視頻解碼器,提供6路模擬輸入和2個增強型的模數轉換器。通過配置SAA7111將PAL制式的模擬基帶信號轉化為ITU-R BT656的4:2:2格式的YUV信號,并將其送入FPGA中進行預處理。經過預處理后的圖像數據再由FPGA重新打包成BT656格式的數據送入到BF561的PPI口。具體連接圖如圖2所示。圖中,VPD[0..7]是數據輸出管腳與FPGA相連,時鐘同步信號BF561采用MDMA的方式將原始圖像信號存入SDRAM中,供視頻跟蹤算法使用。視頻輸出模塊采用飛利浦公司視頻編碼芯片SAA7105將輸出信號轉化為PAL制式的CVBS信號。標準的YUV數據從FPGA的引腳輸出,送到SAA7105的數據管腳上,場、水平和垂直同步信號分別接到FPGA的控制引腳上。SAA7105的參數配置都是通過FPGA產生I2C總線來實現的。

1.2 存儲模塊

BF561的片上存儲器分為兩個部分:每個內核各使用100 KB的專用、高速L1存儲器和128 KB的大容量共享L2存儲器。本系統通過EBIU接口外擴了SDRAM和Flash兩種存儲器。選取2片MT48L32M16A2來構成SDRAM存儲器,μClinux操作系統的映像、圖像處理數據和圖像處理中間結果可存儲在SDRAM中。系統擴展了64 MB的Flash,選用S29GL064M90T芯片存放操作系統的Bootloader和內核程序。

1.3 外圍接口模塊

外圍接口模塊包括串口接口、以太網接口和部分通用接口等。本文主要用到串口接口和以太網接口。串口接口的功能是控制云臺運動,使運動目標隨時在視場范圍內,本文選用MAX488芯片實現BF561內的UART接口的電平轉換;網絡接口的功能是通過系統的嵌入式Web服務器,實現智能監控儀的遠程配置、傳遞監控參數等,采用DM9000即可滿足系統需要。

1.4 DSP雙核以及FPGA之間的通信

在本系統中,涉及到BF561兩個核之間的通信以及BF561與FPGA之間的通信。FPGA給DSP提供圖像數據和經過背景提取之后的二值化圖像數據,DSP將繪制的波門數據傳輸到FPGA,FPGA將波門疊加到原始圖像后送給SAA7105H顯示。常見的雙核通信主要采用中斷、輪詢兩種通信方式[2]。中斷是利用2個核的中斷機制來實現FPGA與DSP之間的通信;輪詢是通過在雙核的共享寄存器里設置一些信號量,供雙核通信與訪問。考慮到本系統的應用條件,本文采用輪詢的通信方式,將信號量定義存放在L2空間。DSP的異步存儲器的地址空間映射到FPGA,通過FPGA操作數據線和地址線,即可完成FPGA與DSP之間的數據交互。

2 軟件算法實現

在本設計中,A核運行μClinux操作系統,B核運行視頻監控算法。μClinux操作系統主要實現以太網芯片DM9000的驅動、Flash的驅動、嵌入式Web服務器BOA的實現和B核的驅動程序。

2.1 算法

本文實現的智能視頻分析儀主要用在視頻監控中,智能視頻監控的核心內容之一是對特定目標進行自動跟蹤。目標跟蹤分為運動目標檢測、行為識別和目標跟蹤3個主要步驟。

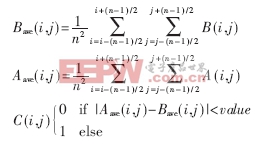

運動目標檢測是從圖像序列中將變化區域從背景圖像中提取出來,本文采用目前最常用的運動檢測算法即背景消除法。此部分算法主要在FPGA中實現,采用基于改進的自適應混合高斯模型的背景建模方法[3]來得到背景圖像。為了節省存儲空間和提高運算速度,在背景建模時,將YUV信號轉化為圖像的灰度值。通過高斯建模得到背景圖像B及原始圖像A后,為了克服樹枝擾動、陽光反射等干擾,采用如下策略進行處理:

評論