基于TMS320DM642 的X264 視頻編碼器的優化

【摘要】簡單介紹了TMS320DM642 數字信號處理器的硬件構成, 簡要給出了DSP 平臺的程序優化一般流程。著重研究了TMS320DM642 平臺優化X264 視頻編碼器,包括算法與系統結構優化,乒乓緩存優化,循環體的優化以及DSP 匯編實現。

1 引言

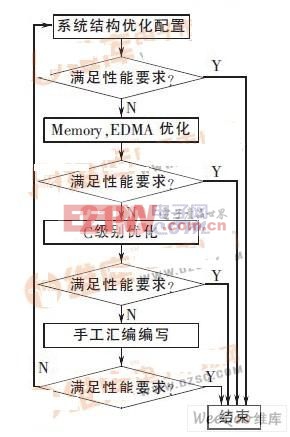

在數字視頻應用方案中,視頻編碼器是核心,其中編碼器的硬件運算能力是系統實時性的保證,而視頻壓縮標準的高壓縮比為編碼器適應各種傳輸帶寬信道提供了必要的保障。視頻編碼工程X264 是一款開源的、按照H.264 標準在PC 平臺開發的視頻編碼器, 如果直接移植到TMS320DM642(以下簡稱DM642)平臺,則實際的編碼速度一般低于視頻應用方案所需要的實時性要求。為了提高編碼工程的編碼速度, 需要對移植到DM642 平臺的X264 進行優化, 整個優化的流程如圖1所示。

圖1 優化流程圖

2 DM642 硬件介紹

DM642 采用TI 開發的第二代高性能先進VelociTI技術的VLIW 架構VelociTI1.2,在主頻600 MHz 下處理速度達到4 800 MI/s(兆指令/秒)。DM642 CPU 核內部具有64 個32 位通用寄存器和8 個獨立的32 位運算單元(2 個乘法器和6 個算數邏輯單元), 確保每個周期能夠提供4 個16 位介質訪問控制(Medium Access Control,MAC)。

評論